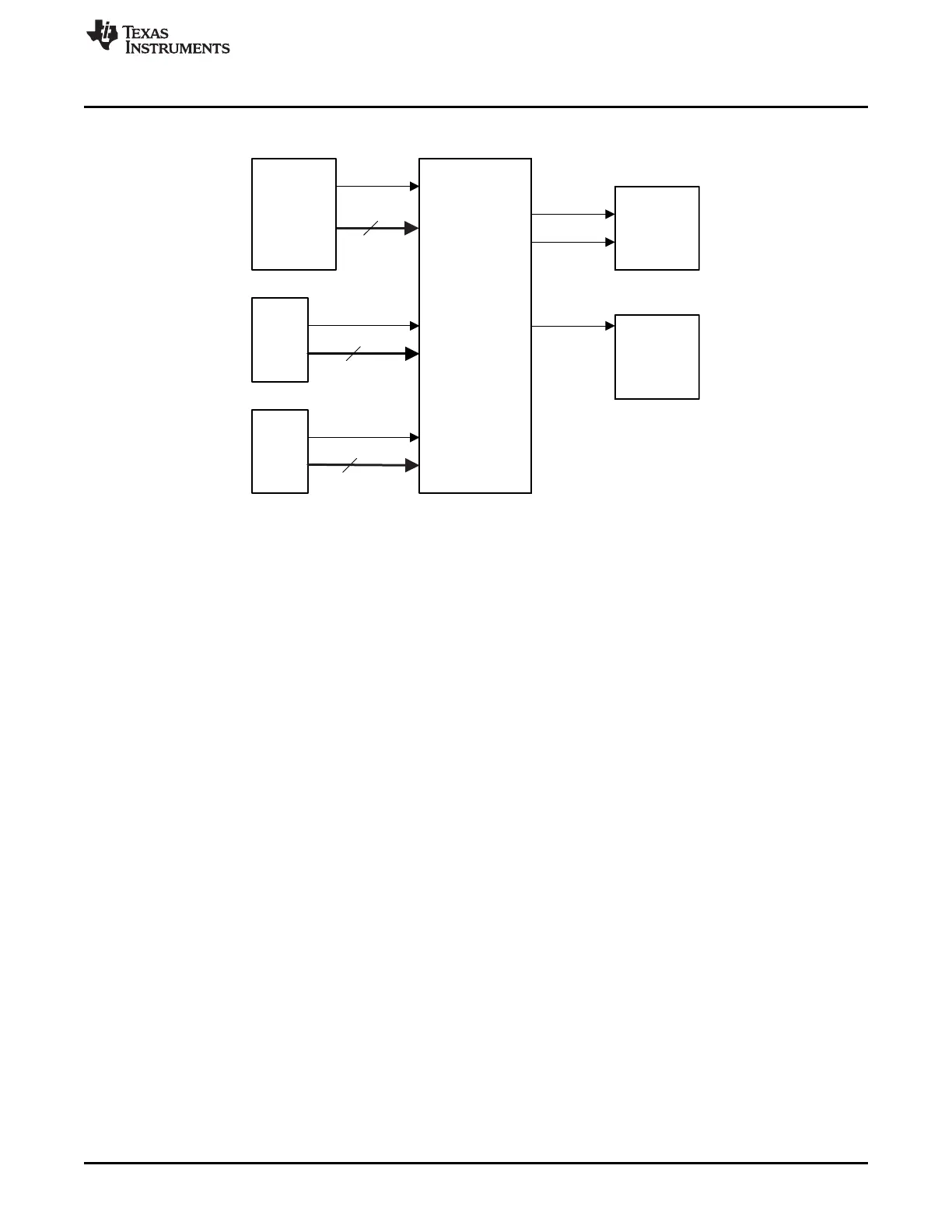

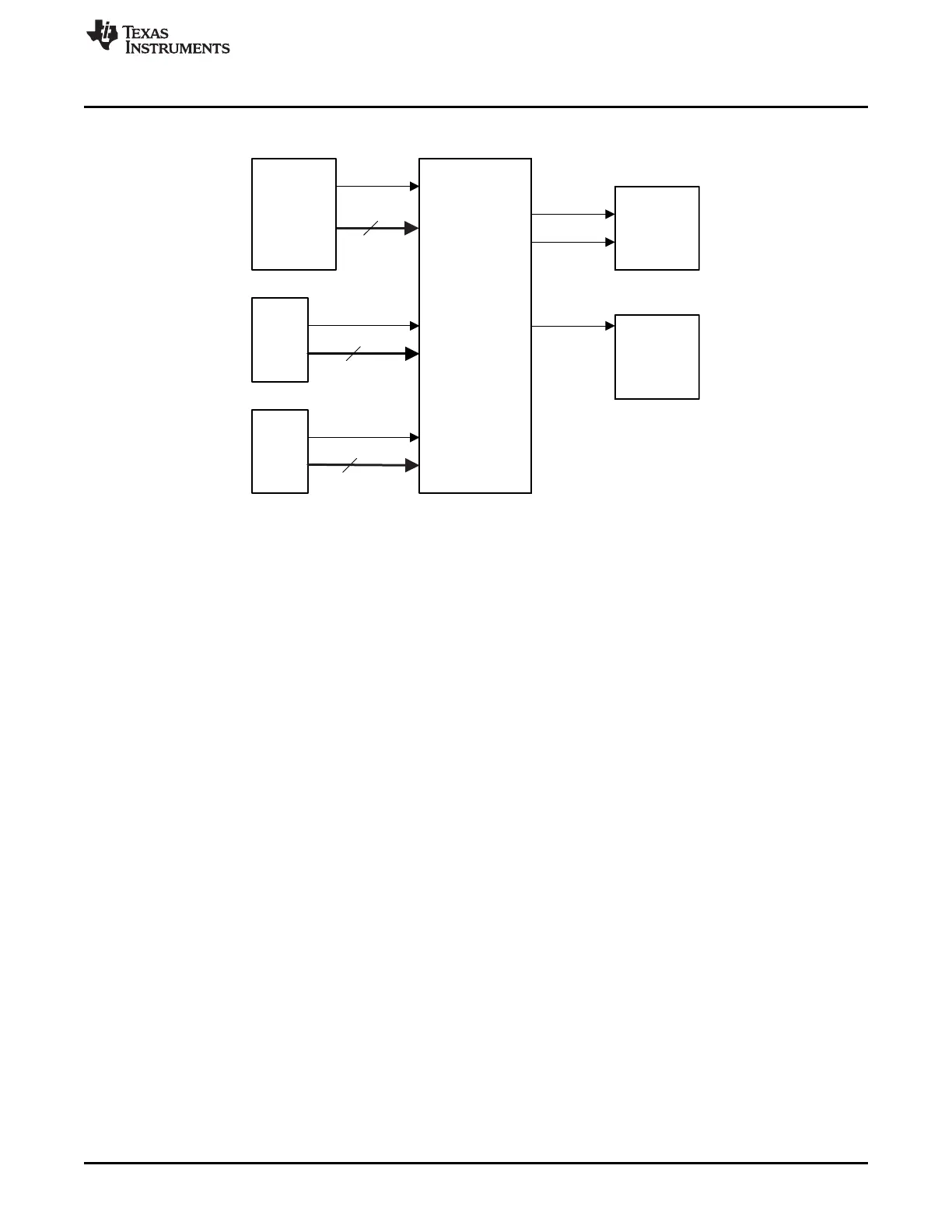

CPU

IP0

IP1

EPC

ESM

serr_event

uerr_event

serr_valid

serr_addr

32

serr_valid

serr_addr

32

uerr_valid

uerr_addr

32

cam_fifo_full_int

VIM

www.ti.com

Module Operation

485

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Error Profiling Controller (EPC)

Figure 12-1. EPC System Block Diagram

12.2.1 Uncorrectable Fault Operation

EPC will capture full 32-bit addresses of uncorrectable fault from interconnect and RAM IP modules to

UERRADDR_(0,1) registers and set the corresponding uncorrectable status bit in UERRSTAT register.

The first uncorrectable address from RAM and interconnect IP will be captured to the corresponding

UERRADDR_(0,1) and frozen until CPU in privilege mode write clears to the corresponding UERRSTAT

bit.

Whenever any status bit in ERRSTAT just got set by the presence of a new uncorrectable fault, EPC will

trigger uncorrectable fault event to ESM. The bits in UERRSTAT can only be cleared by device power on

reset or CPU write clears in privilege mode.

12.2.2 Correctable Fault Operation

12.2.2.1 Functional Mode

CPU, Interconnect, and RAM IP can trigger correctable fault event to EPC. The EPC provides a 4-entry

FIFO to each of these IP(s) to capture correctable event and its 64-bit aligned addresses.

A FIFO full condition happens when all 4 entries of a particular FIFO are occupied. In this case, the

corresponding FIFO full status bit of the IP will be set in FIFOFULLSTAT register. An interrupt will be

generated if CAMFIFOFULLENA bit is set in EPCCNTRL register.

A FIFO overflow can happen when all entries are occupied and there is a new correctable fault event just

arrives to the same FIFO. In this case, the new correctable fault event and address will be discarded, but

the overflow bit remained to be set. If the SERRENA bits in EPCCNTRL register are enabled, the single-

bit error correctable fault event will be triggered to ESM.

A FIFO full or overflow interrupt indicates to you that there is an abnormal condition on the number of

correctable faults happening to the particular IP. It is up to application software to handle this situation by

either putting the system in safe stage if the IP causing full or overflow interrupt happens to be a critical IP

in safety application or doing extra diagnostic of the corresponding IP memory during diagnostic time. You

can write clears the corresponding FIFO full or overflow status bit in privilege mode.

Loading...

Loading...