www.ti.com

SCM Registers

263

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

SCR Control Module (SCM)

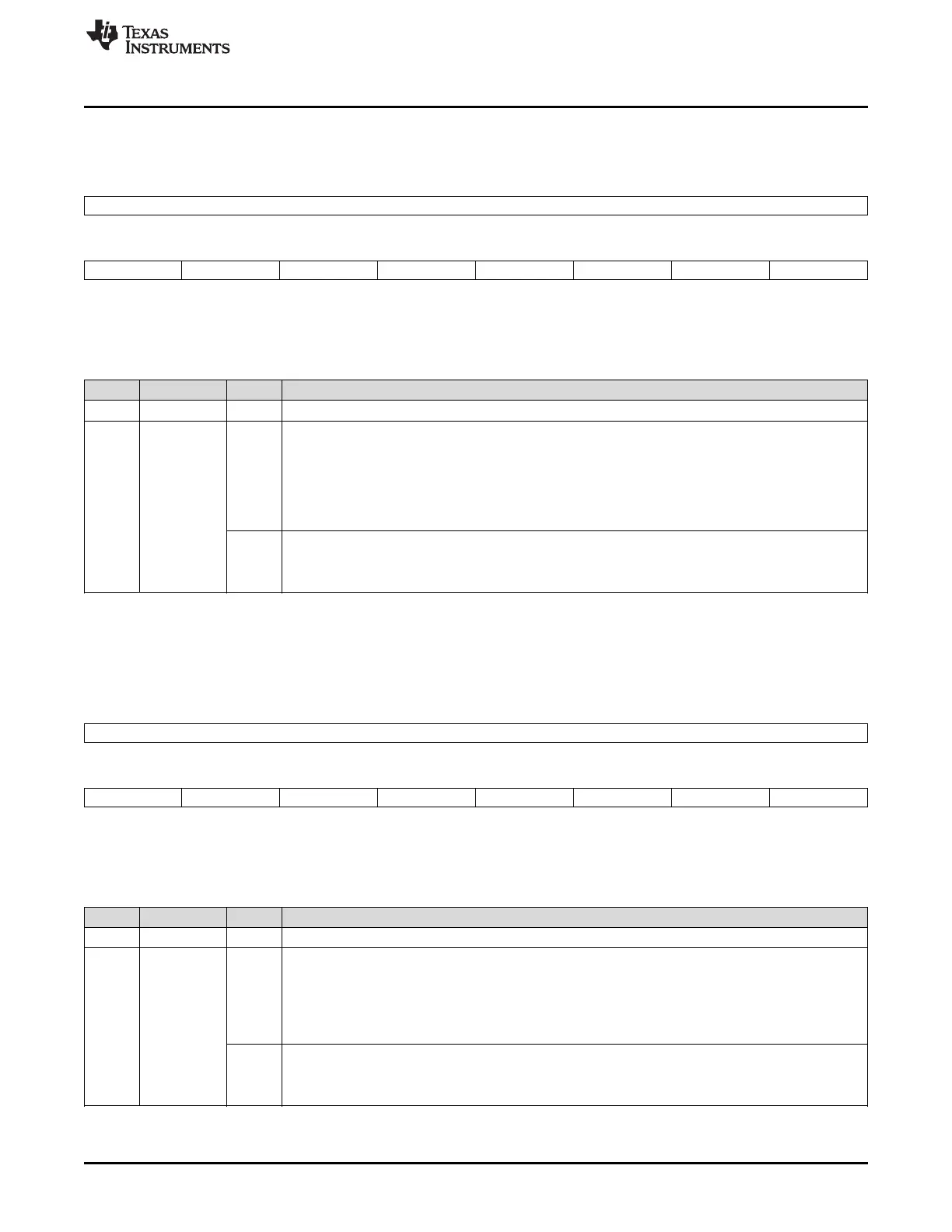

3.4.4 SCM Initiator Error0 Status Register (SCMIAERR0STAT)

Figure 3-8. SCM Initiator Error0 Status Register (SCMIAERR0STAT) [offset = 10h]

31 8

Reserved

R-0

7 6 5 4 3 2 1 0

R2A7 R2A6 R2A5 R2A4 R2A3 R2A2 R2A1 R2A0

R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0

LEGEND: R/W = Read/Write; W1CP = Write 1 to clear in privilege mode only; -n = value after synchronous reset by power-on reset

Table 3-5. SCM Initiator Error0 Status Register (SCMIAERR0STAT) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved. Read returns 0.

7-0 R2An Request to Acceptance Timeout Error happens on IAn. Each bit n corresponds to request to accept

time out error occurred for each IA. Refer to Interconnect chapter of the TRM for specific mapping of

each R2An to a particular IP.

Read:

0 No request to accept time out error happens on IAn.

1 Request to accept time out error happens on IAn.

Write in Privilege:

0 No effect.

1 Clear this flag bit.

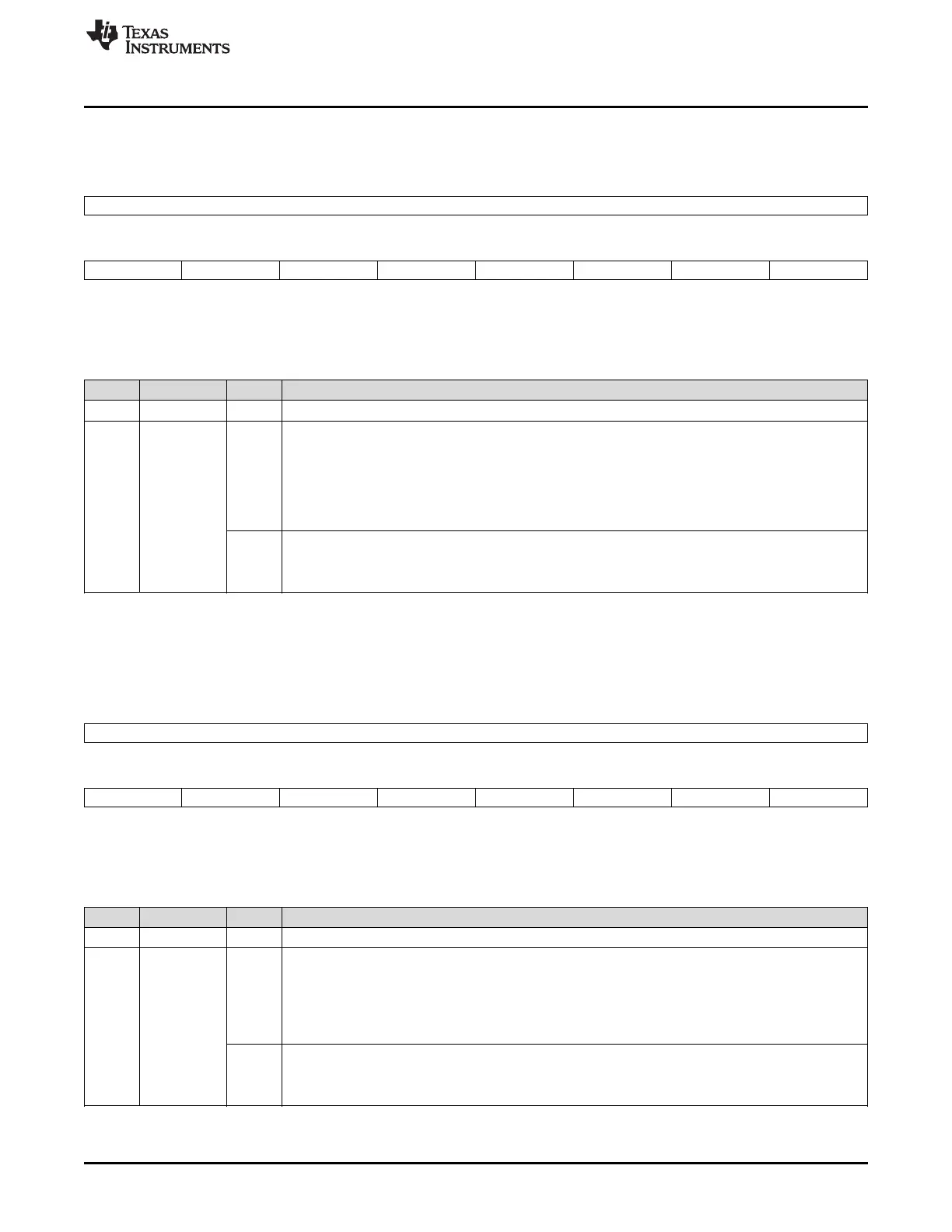

3.4.5 SCM Initiator Error1 Status Register (SCMIAERR1STAT)

Figure 3-9. SCM Initiator Error1 Status Register (SCMIAERR1STAT) [offset = 14h]

31 8

Reserved

R-0

7 6 5 4 3 2 1 0

R2R7 R2R6 R2R5 R2R4 R2R3 R2R2 R2R1 R2R0

R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0

LEGEND: R/W = Read/Write; W1CP = Write 1 to clear in privilege mode only; -n = value after synchronous reset by power-on reset

Table 3-6. SCM Initiator Error1 Status Register (SCMIAERR1STAT) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved. Read returns 0.

7-0 R2Rn Request to Response Timeout Error happens on IAn. Each bit n corresponds to request to response

time out error occurred for each IA.. Refer to Interconnect chapter of the TRM

Read:

0 No request to response time out error happens on IAn.

1 Request to response time out error happens on IAn.

Write in Privilege:

0 No effect.

1 Clear this flag bit.

Loading...

Loading...