HWAG Registers

www.ti.com

1050

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

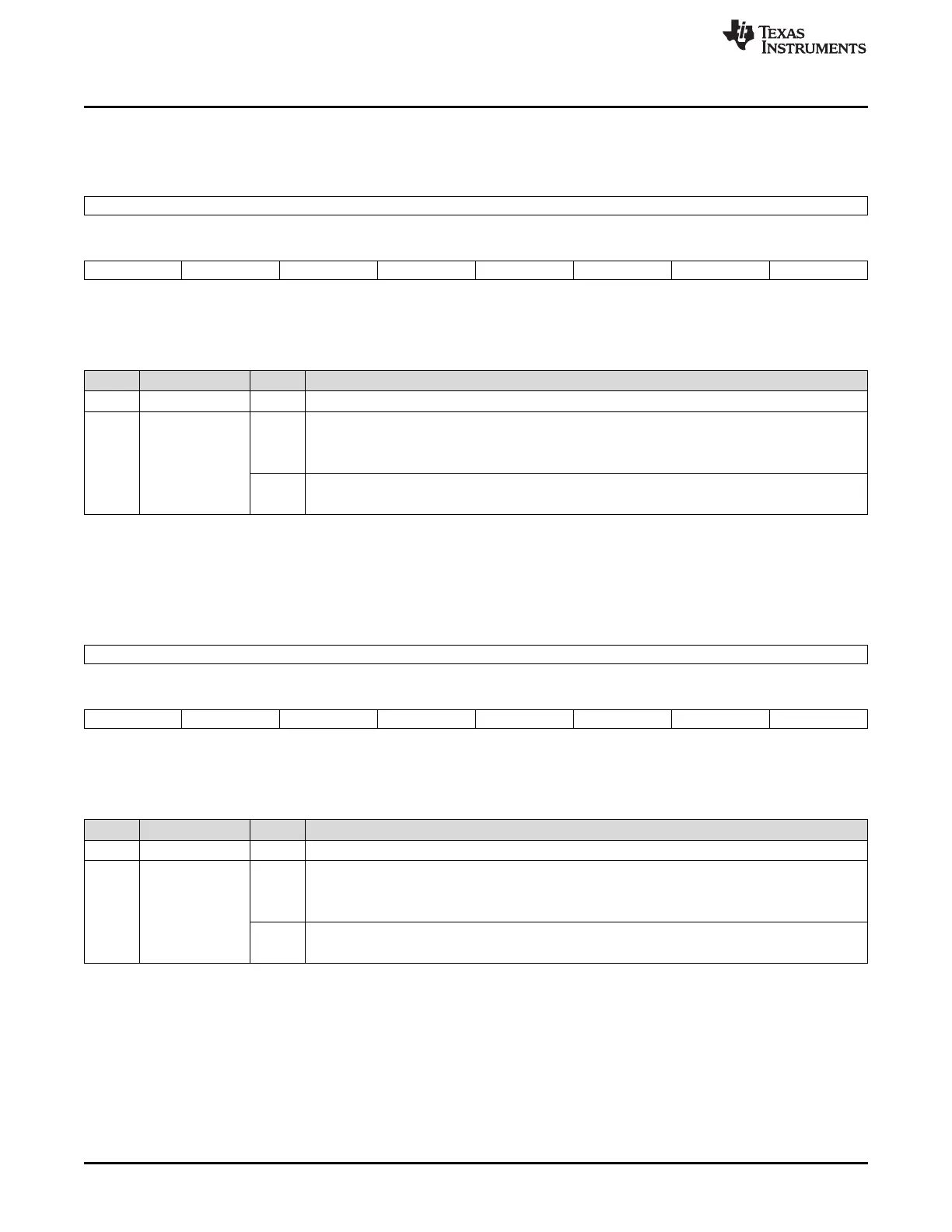

23.5.7 HWAG Interrupt Level Set Register (HWALVLSET)

Figure 23-95. HWAG Interrupt Level Set Register (HWALVLSET)

31 8

Reserved

R-0

7 6 5 4 3 2 1 0

SETINTLVL7 SETINTLVL6 SETINTLVL5 SETINTLVL4 SETINTLVL3 SETINTLVL2 SETINTLVL1 SETINTLVL0

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 23-59. HWAG Interrupt Level Set Register (HWALVLSET) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reads return 0. Writes have no effect.

7-0 SETINTLVL[n] Set Interrupt Level. See Table 23-57.

0 Read: Low-priority interrupt.

Write: No effect.

1 Read: High-priority interrupt.

Write: Set interrupt priority to high.

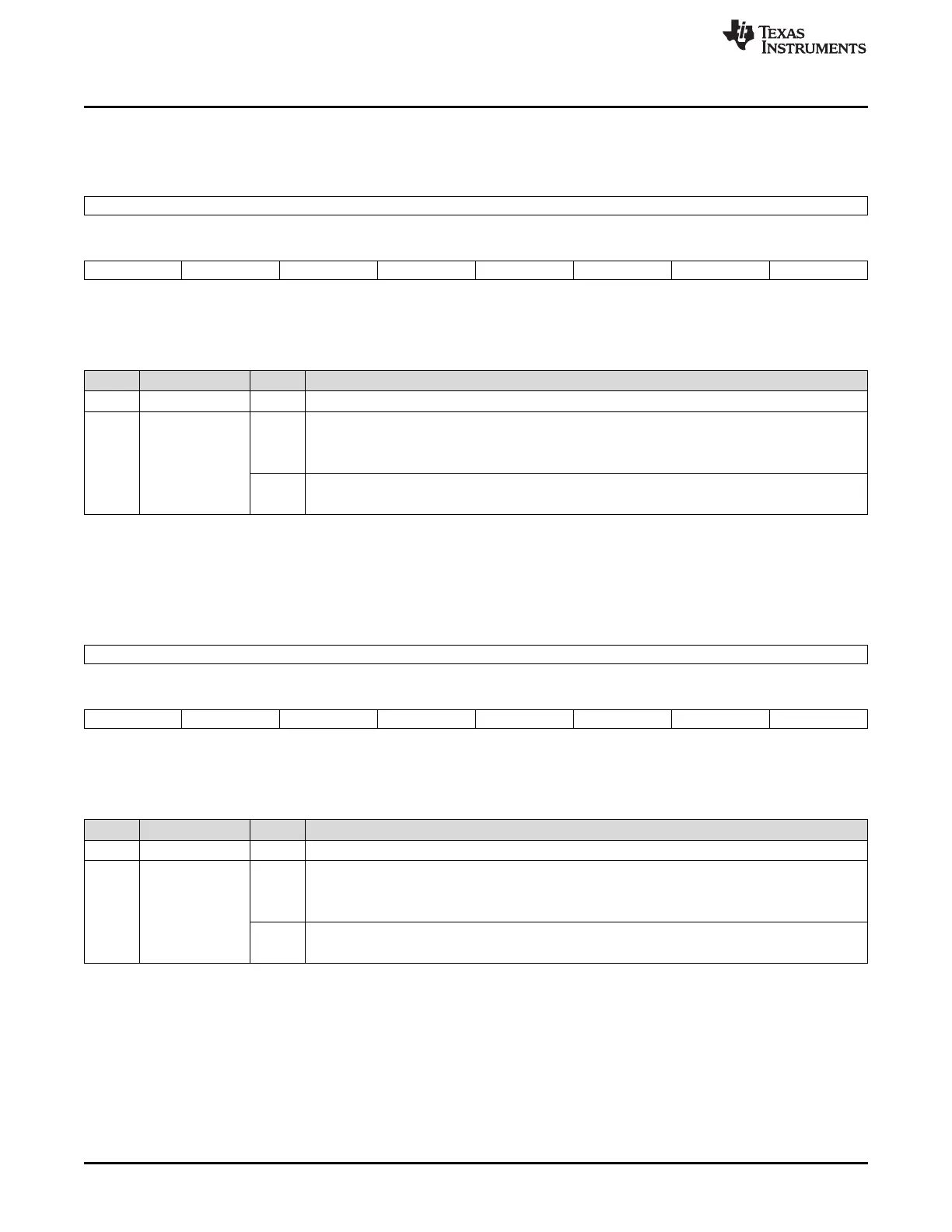

23.5.8 HWAG Interrupt Level Clear Register (HWALVLCLR)

Figure 23-96. HWAG Interrupt Level Clear Register (HWALVLCLR)

31 8

Reserved

R-0

7 6 5 4 3 2 1 0

CLRINTLVL7 CLRINTLVL6 CLRINTLVL5 CLRINTLVL4 CLRINTLVL3 CLRINTLVL2 CLRINTLVL1 CLRINTLVL0

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 23-60. HWAG Interrupt Level Clear Register (HWALVLCLR) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reads return 0. Writes have no effect.

7-0 CLRINTLVL[n] Clear Interrupt Level. See Table 23-57.

0 Read: Low-priority interrupt.

Write: No effect.

1 Read: High-priority interrupt.

Write: Set interrupt priority to low.

Loading...

Loading...