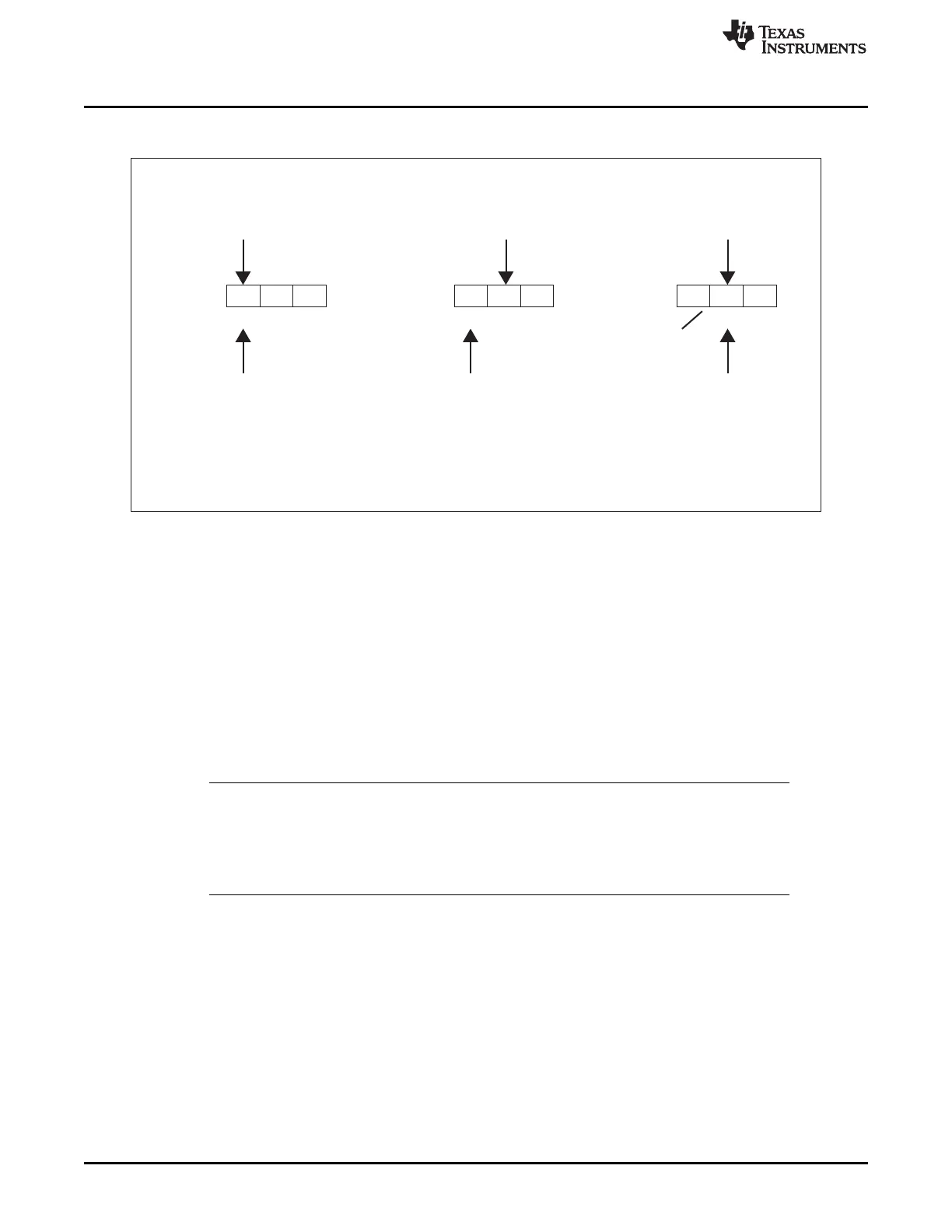

1 2 3

A - -

Buffers

Messages

1 2 3

A B C

Buffers

Messages

1 32

- - -

Buffers

Messages

PIDX

(store next)

GIDX

(read oldest)

GIDX

(read oldest)

GIDX

(read oldest)

PIDX

(store next)

PIDX

(store next)

- PIDX incremented last

- Next received message

will be stored into buffer 1

- If buffer 1 has not been read

before message A is lost

D

FIFO empty FIFO not empty FIFO overrun

Module Operation

www.ti.com

1250

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

Figure 26-16. FIFO Status: Empty, Not Empty, and Overrun

26.2.11.2 Configuration of the FIFO

(Re)configuration of message buffers belonging to the FIFO is only possible when the Communication

Controller is in DEFAULT_CONFIG or CONFIG state. While the Communication Controller is in

DEFAULT_CONFIG or CONFIG state, the FIFO function is not available.

For all message buffers belonging to the FIFO should have the same payload length configured in

WRHS2.PLC(6-0) of the Write Header Section 2 register. The data pointer to the first 32-bit word in the

data section of the corresponding message buffer has to be configured by WRHS3.DP(10-0).

All information required for acceptance filtering is taken from the FIFO rejection filter and the FIFO

rejection filter mask. With the exception of DP and PLC, the values configured in the header sections of

the message buffers belonging to the FIFO are irrelevant.

NOTE: It is recommended to program the MBI bits of the message buffers belonging to the FIFO to

0 by WRHS1.MBI to avoid RX interrupts to be generated.

If the payload length of a received frame is longer than the value programmed by

WRHS2.PLC(6-0) in the header section of the corresponding message buffer, the data field

stored in a message buffer of the FIFO is truncated to that length.

26.2.11.3 Access to the FIFO

For FIFO access outside DEFAULT_CONFIG and CONFIG state, the Host has to trigger a transfer from

the Message RAM to the Output Buffer by writing the number of the first message buffer of the FIFO

(referenced by MRC.FFB(7-0)) to the Output Buffer Command Request (OBCR) register. The message

handler then transfers the message buffer addressed by the GET Index register (GIDX) to the output

buffer. After this transfer the GET Index register (GIDX) is incremented.

26.2.12 Message Handling

The message handler controls data transfers between the input / output buffer and the message RAM and

between the message RAM and the two transient buffer RAMs. All accesses to the internal RAMs are 32

bit accesses.

Loading...

Loading...