www.ti.com

CPU Interconnect Subsystem

271

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Interconnect

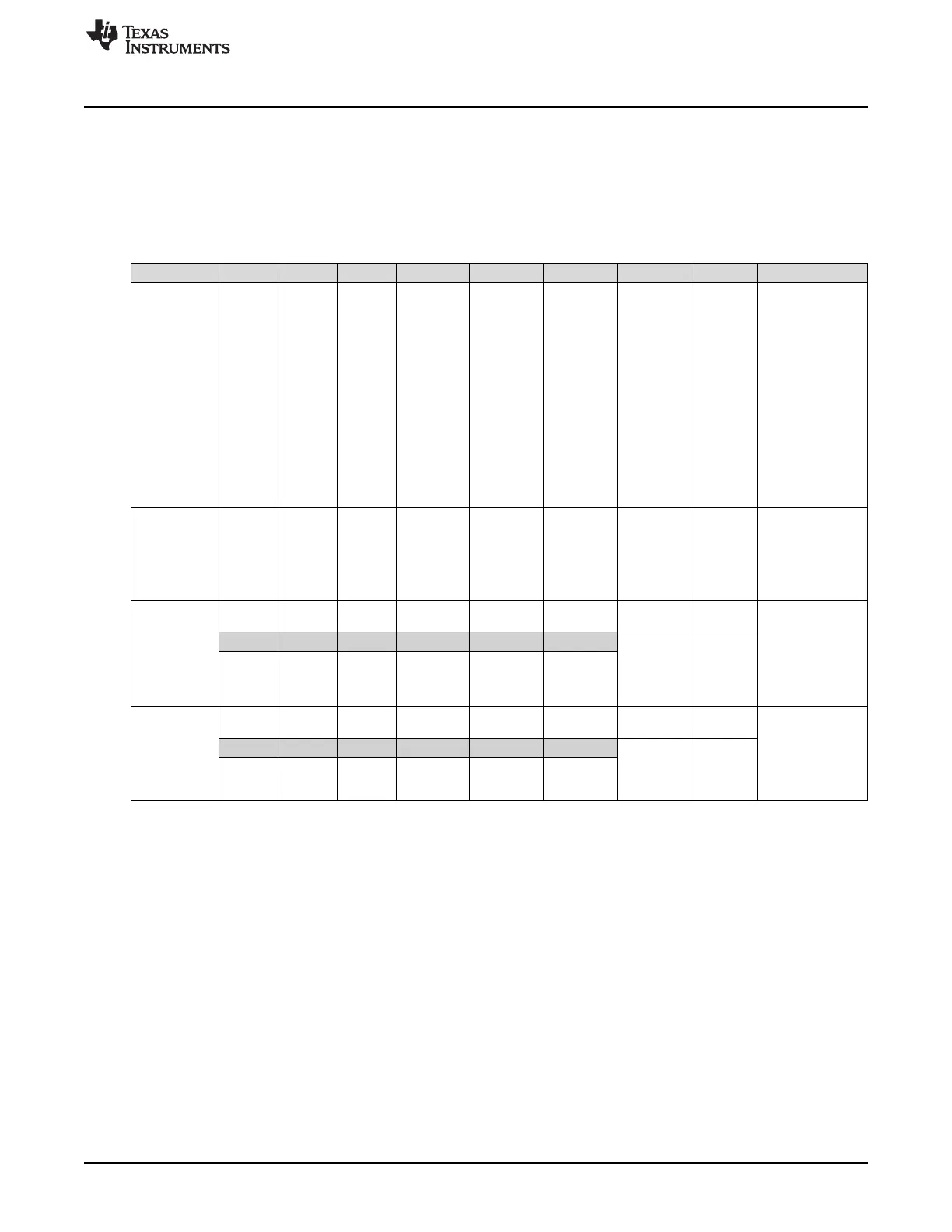

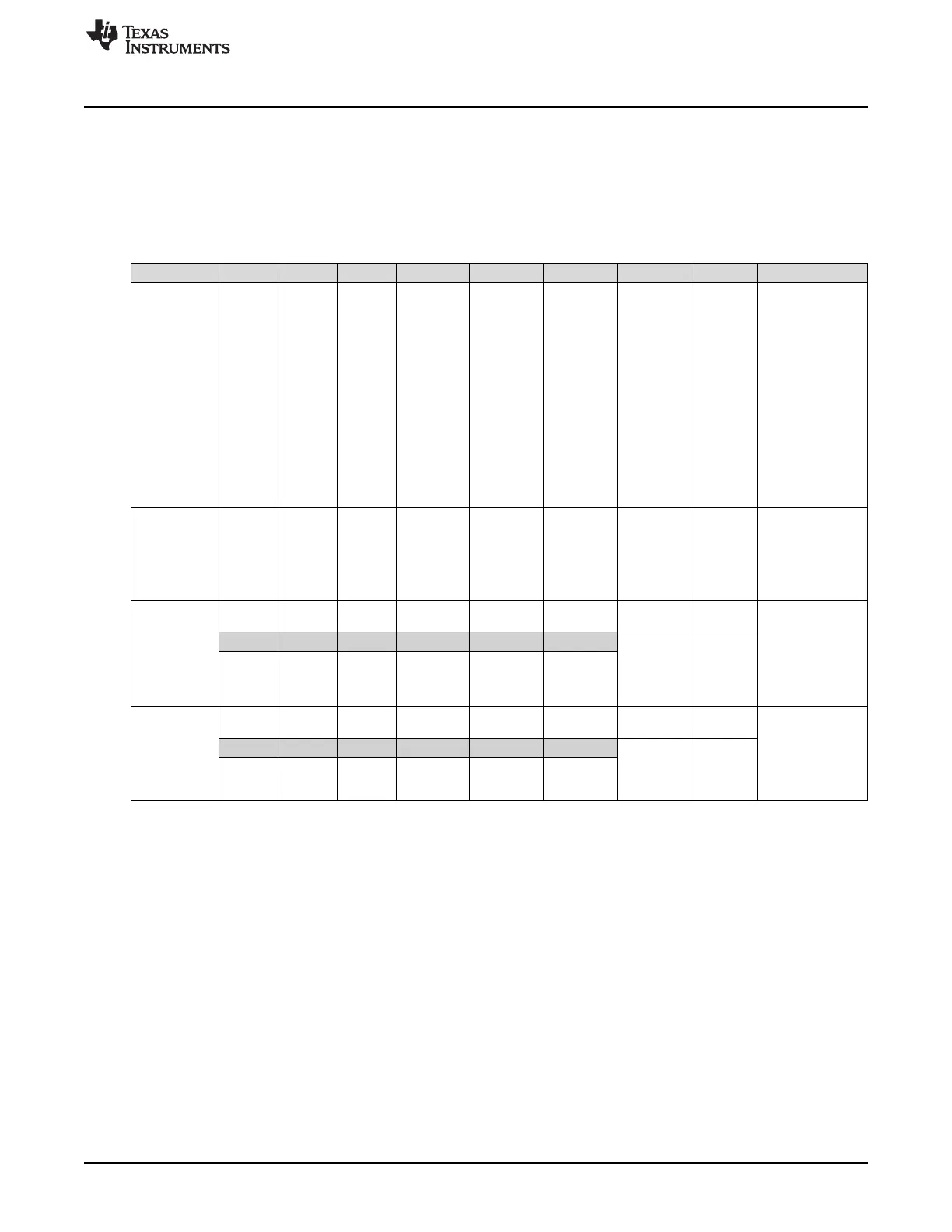

4.3.6 Interconnect Runtime Status

Both the CPU Interconnect Subsystem and the Peripheral Interconnect Subsystem will output its status on

each master and slave interface to the SCM indicating if the interface is currently active. The status are

captured in the SCMIASTAT register for the master interfaces and SCMTASTAT for the slave interfaces.

See Table 4-4 for the mapping between each interface to each bit field.

Table 4-4. SCM Register Bit Mapping

Register Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 Remark

SCMIAERR0

STAT

PS_SCR

_M

POM

DMA

Port A

Reserved Reserved

CPU AXI-M

Read

CPU AXI-M

Write

ACP-M

Each bit indicates

the transaction

processing block

inside the

interconnect

corresponding to the

master that is

detected by the

interconnect checker

to have a fault.

A timeout error

when the time the

request is issued by

the master until the

time the request is

accepted by the

slave has expired

SCMIAERR1

STAT

PS_SCR

_M

POM

DMA

Port A

Reserved Reserved

CPU AXI-M

Read

CPU AXI-M

Write

ACP-M

A timeout error

when the time the

request is accepted

by the slave until the

time the request is

responded by the

slave has expired

SCMIASTAT

PS_SCR

_M

POM

DMA

Port A

Reserved Reserved

CPU AXI-M

Read

CPU AXI-M

Write

ACP-M

Each bit indicates

that there is still

pending transactions

for the

corresponding

master to be

processed by the

interconnect

Bit 8 Bit 9 Bit 10 Bit 11 Bit 12 Bit 13

DMA

PortB

HTUx/

FTU

DAP/

DMM

Ethernet CPU PP-AXI Reserved

SCMTASTAT

L2 RAM

L2 Flash

Port B

L2 Flash

Port A

EMIF Reserved CPU AXI-S ACP-S

PS_SCR

_S

Each bit indicates

that there is still

pending transactions

for the

corresponding slave

to be processed by

the interconnect

Bit 8 Bit 9 Bit 10 Bit 11 Bit 12 Bit 13

PCR1 PCR2 PCR3 CRC1 CRC2 SDC MMR

Loading...

Loading...