www.ti.com

N2HET Control Registers

1037

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

23.4.26 Parity Control Register (HETPCR)

N2HET1: offset = FFF7 B874h; N2HET2: offset = FFF7 B974h

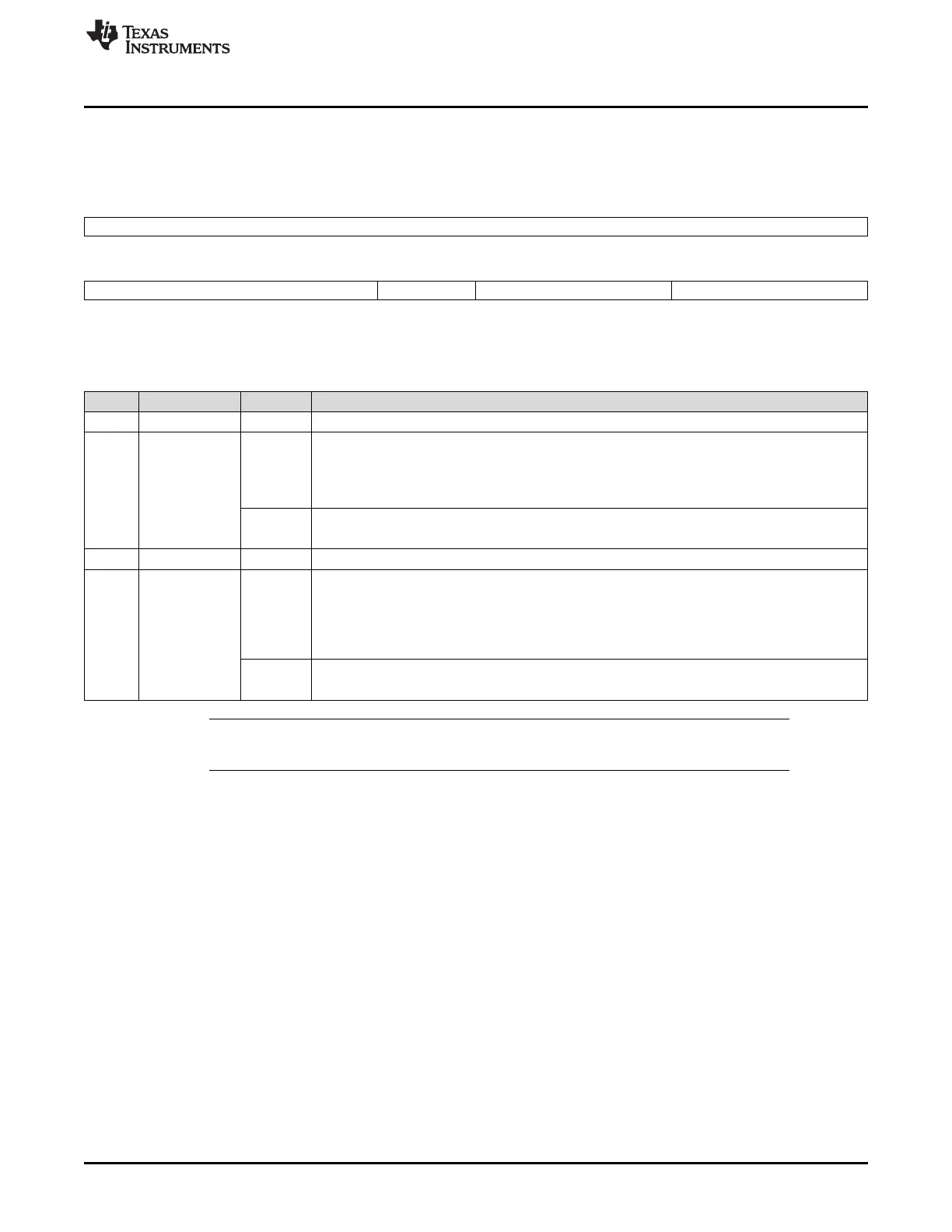

Figure 23-81. Parity Control Register (HETPCR)

31 16

Reserved

R-0

15 9 8 7 4 3 0

Reserved TEST Reserved PARITY_ENA

R-0 R/WP-0 R-0 R/WP-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

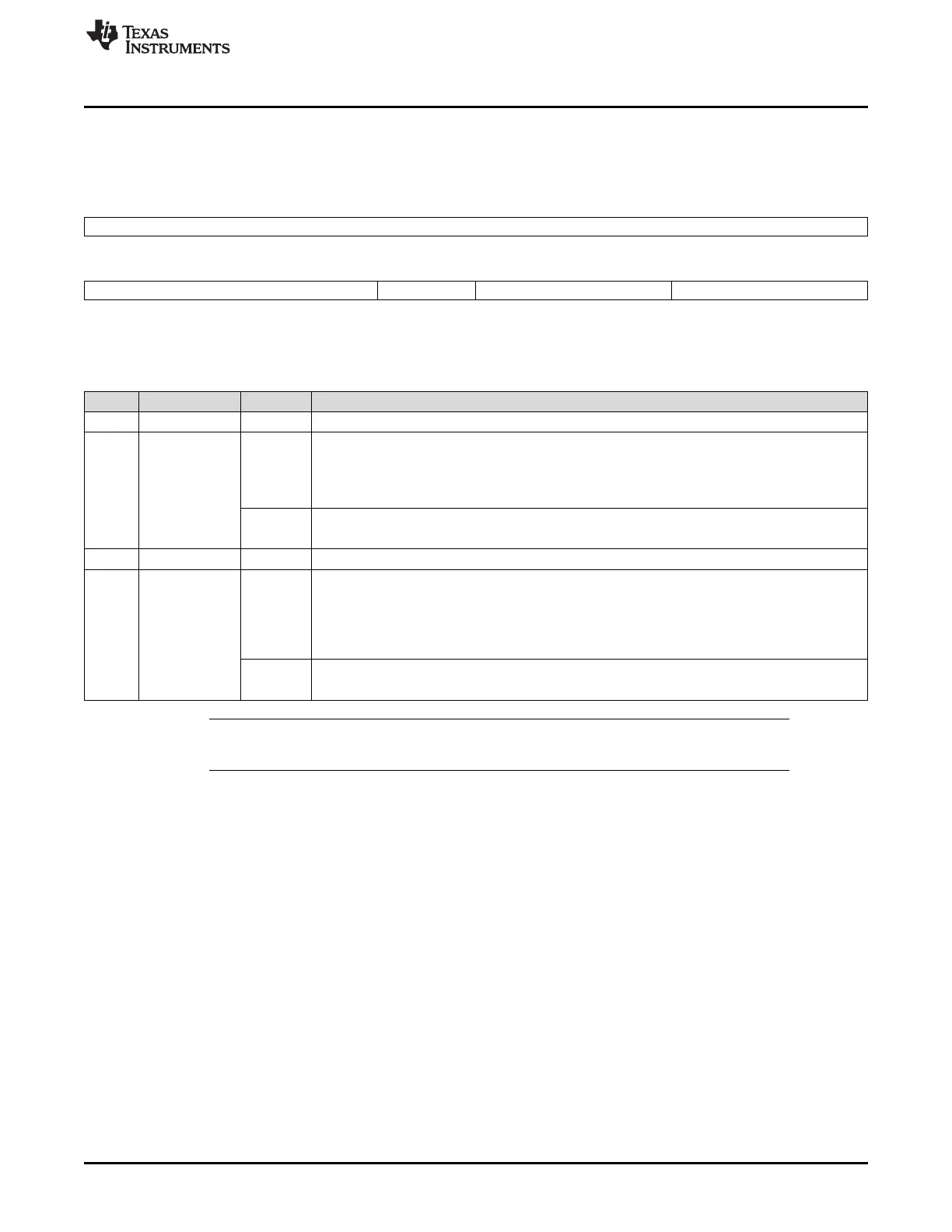

Table 23-42. Parity Control Register (HETPCR) Field Descriptions

Bit Field Value Description

31-9 Reserved 0 Reads return 0. Writes have no effect.

8 TEST Test Bit. When this bit is set, the parity bits are mapped into the peripheral RAM frame to make

them accessible by the CPU.

0 Read: Parity bits are not memory mapped.

Write: Disable mapping.

1 Read: Parity bits are memory mapped.

Write: Enable mapping.

7-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 PARITY_ENA Enable/disable parity checking. This bit field enables or disables the parity check on read

operations and the parity calculation on write operations. If parity checking is enabled and a parity

error is detected the N2HET_UERR signal is activated.

5h Read: Parity check is disabled.

Write: Disable checking.

Others Read: Parity check is enabled.

Write: Enable checking.

NOTE: It is recommended to write Ah to enable error detection, to guard against soft errors flipping

PARITY_ENA to a disable state.

Loading...

Loading...