N2HET Control Registers

www.ti.com

1018

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

23.4.1 Global Configuration Register (HETGCR)

N2HET1: offset = FFF7 B800h; N2HET2: offset = FFF7 B900h

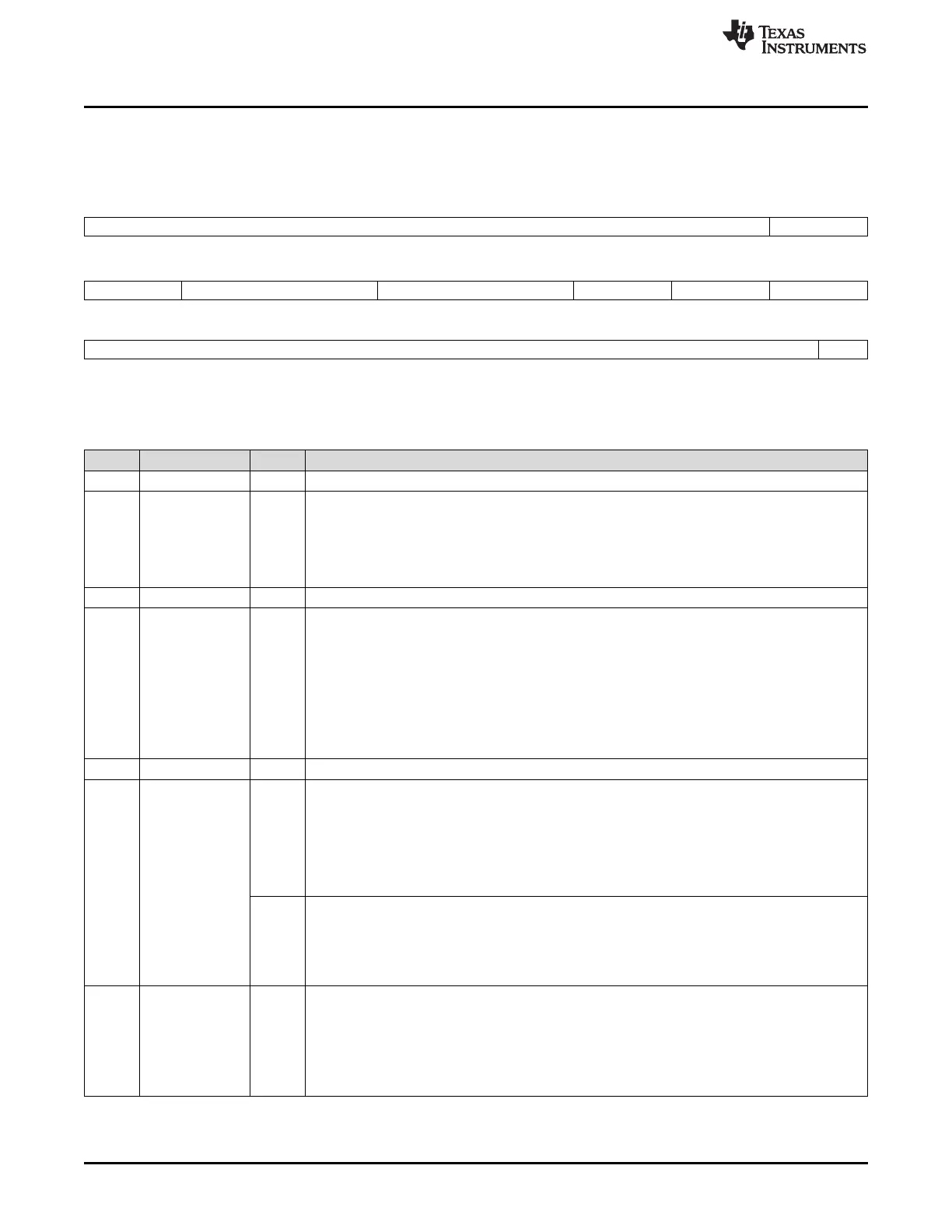

Figure 23-56. Global Configuration Register (HETGCR) [offset = 00h]

31 25 24

Reserved HET_PIN_ENA

R-0 R/W-1

23 22 21 20 19 18 17 16

Reserved MP Reserved PPF IS CMS

R-0 R/W-0 R-0 R/W-0 R/W-0 R/W-0

15 1 0

Reserved TO

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

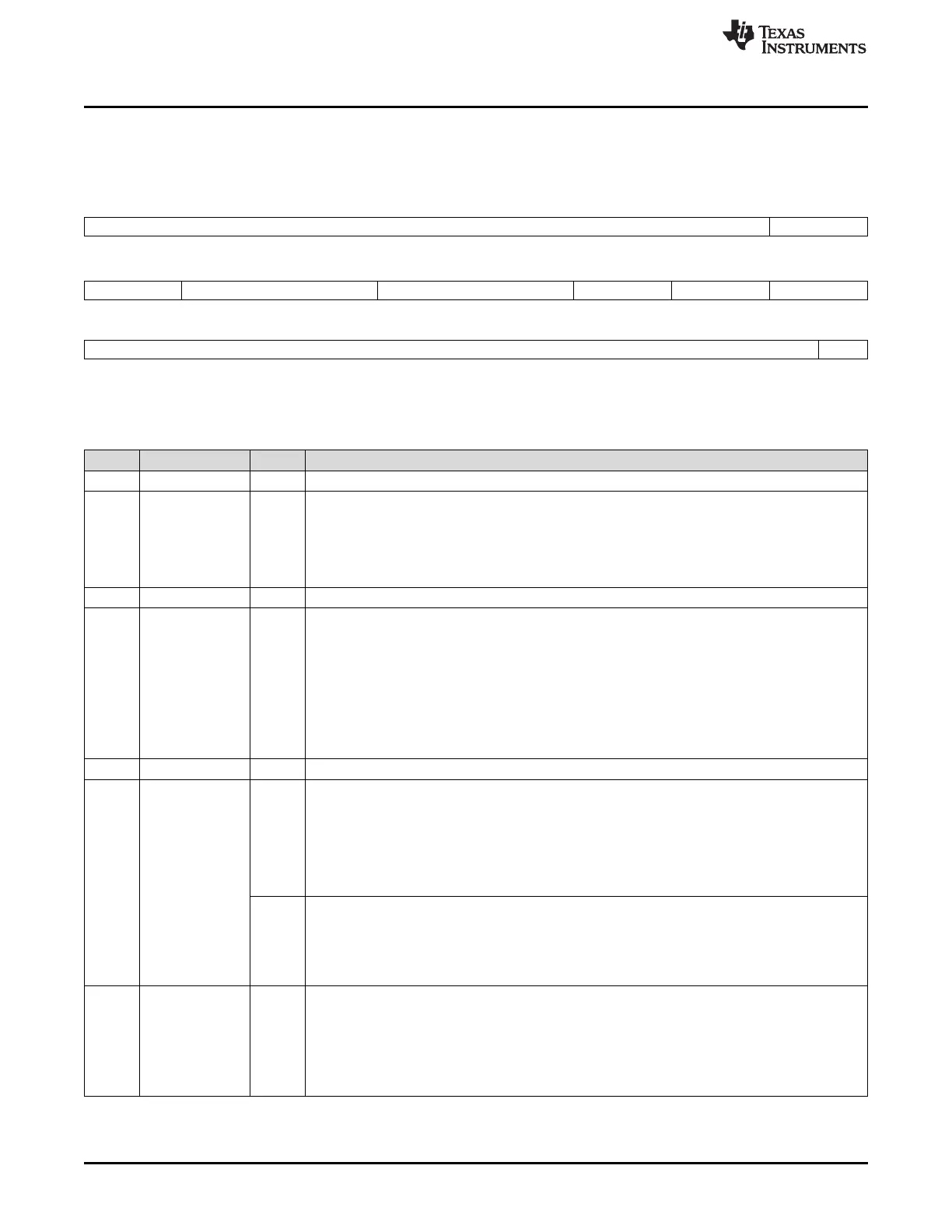

Table 23-16. Global Configuration Register (HETGCR) Field Descriptions

Bit Field Value Description

31-25 Reserved 0 Reads return 0. Writes have no effect.

24 HET_PIN_ENA Enables the output buffers of the pin structures depending on the value of nDIS and DIR.x when

PINDIS.x is set.

Note: This bit will automatically get cleared when nDIS pin (input port) value is 0.

0 No affect on the pin output buffer structure.

1 Enables the pin output buffer structure when DIR = output, PINDIS.x is set and nDIS = 1.

23 Reserved 0 Reads return 0. Writes have no effect.

22-21 MP Master Priority

The NHET can prioritize master accesses to N2HET RAM between the HET Transfer Unit and

another arbiter, which outputs the access of one of the remaining masters. The MP bits allow the

following selections:

0 The HTU has lower priority to access the N2HET RAM than the arbiter output.

1h The HTU has higher priority to access the N2HET RAM than the arbiter output.

2h The HTU and the arbiter output use a round robin scheme to access the N2HET RAM.

3h Reserved

20-19 Reserved 0 Reads return 0. Writes have no effect.

18 PPF Protect Program Fields

The PPF bit together with the Turn On/Off bit (TO) allows to protect the program fields of all

instructions in N2HET RAM.

When TO = 0:

0 All masters can read and write the program fields.

1 All masters can read and write the program fields.

When TO = 1:

0 All masters can read and write the program fields.

1 The program fields are readable but not writable for all masters, which could access the N2HET

RAM. Possible masters are the CPU, HTU, DMA and a secondary CPU (if available). Writes

initiated by these masters are discarded.

17 IS Ignore Suspend

When Ignore Suspend = 0, the timer operation is stopped on suspend (the current timer instruction

is completed). Timer RAM can be freely accessed during suspend. When set to 1, the suspend is

ignored and the N2HET continues operating.

0 N2HET stops when in suspend mode.

1 N2HET ignores suspend mode and continues operation.

Loading...

Loading...