www.ti.com

N2HET Control Registers

1039

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

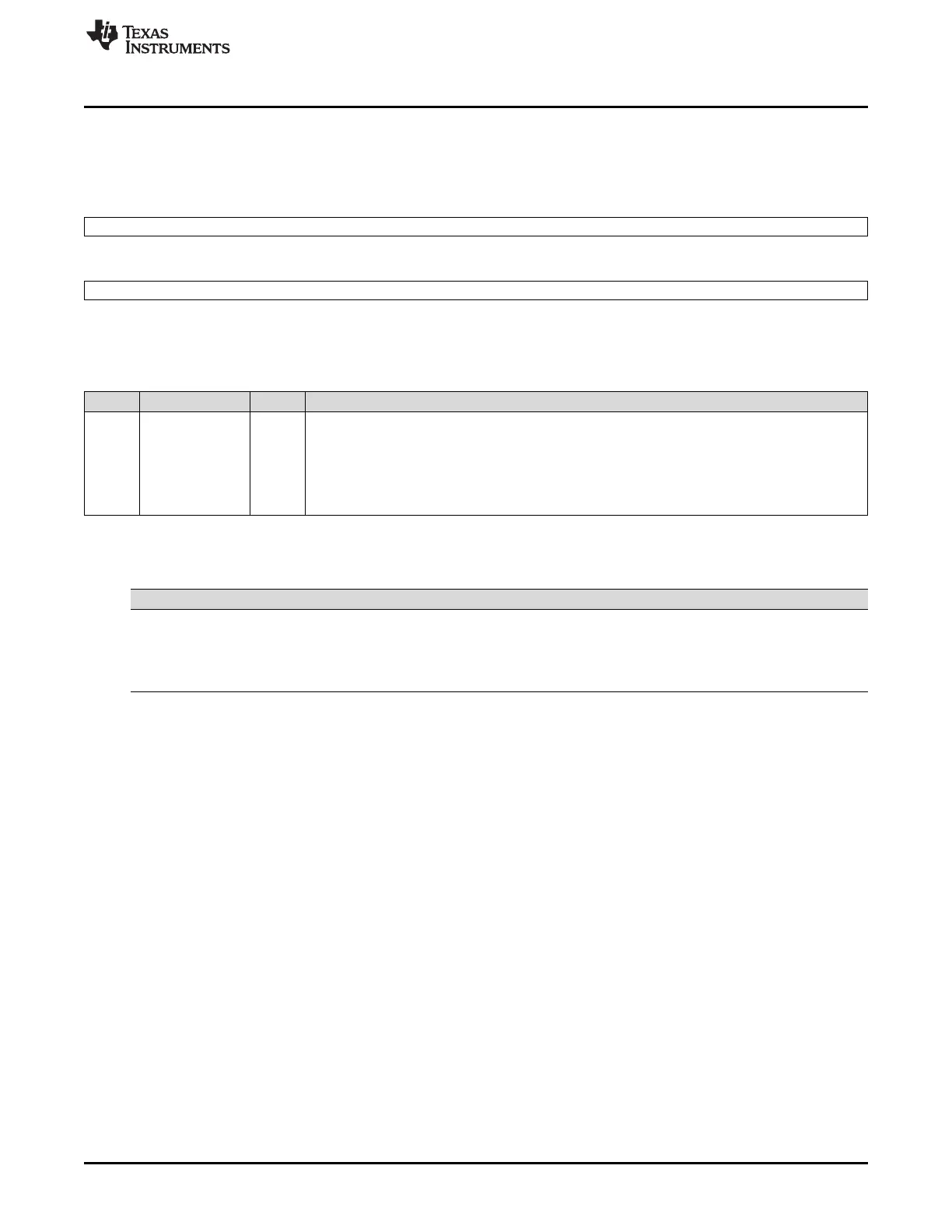

23.4.28 Parity Pin Register (HETPPR)

N2HET1: offset = FFF7 B87Ch; N2HET2: offset = FFF7 B97Ch

Figure 23-83. Parity Pin Register (HETPPR)

31 16

HETPPR

R/W-0

15 0

HETPPR

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

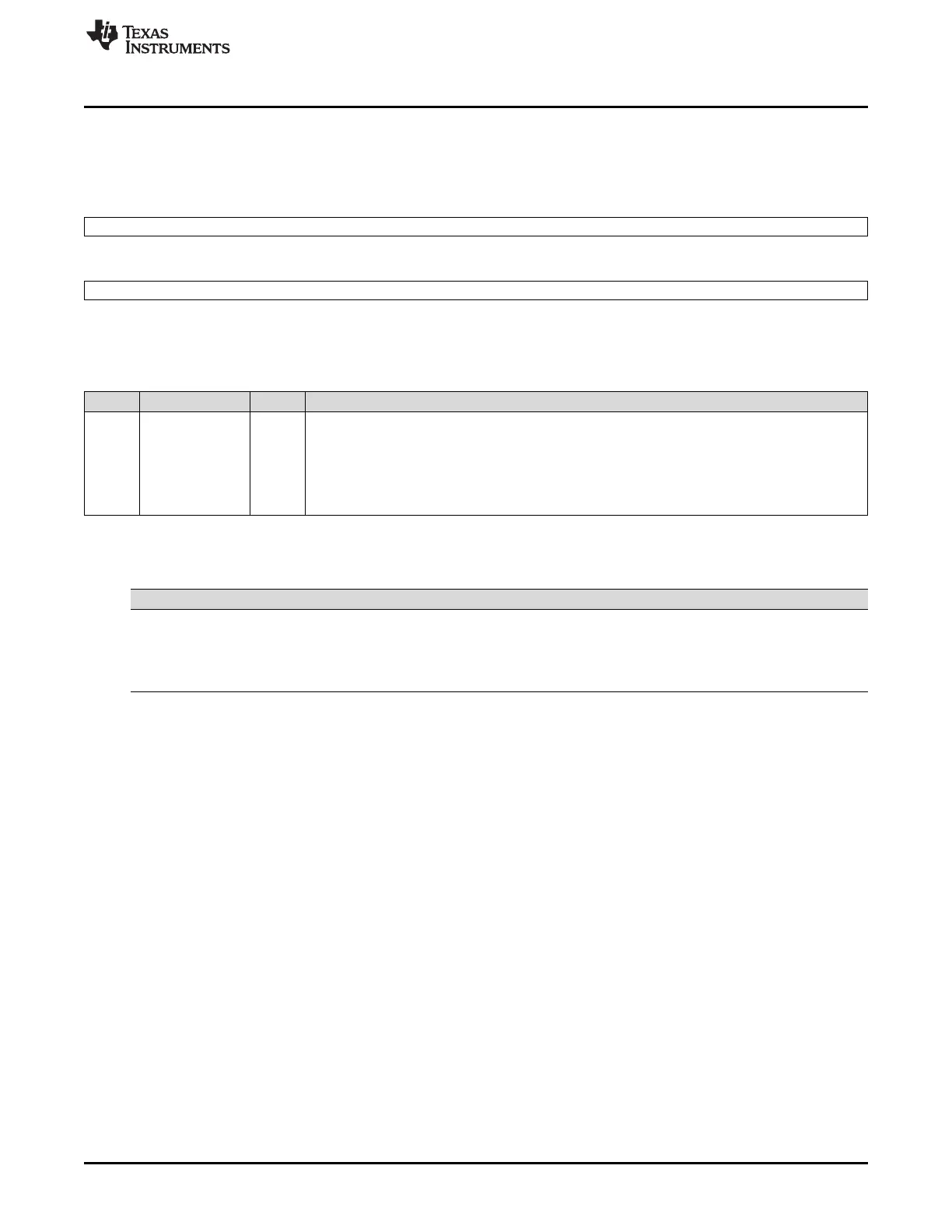

Table 23-44. Parity Pin Register (HETPPR) Field Descriptions

Bit Field Value Description

31-0 HETPPR[n] NHET Parity Pin Select Bits. Allows HET[n] pins to be configured to drive to a known state when an

N2HET parity error is detected.

0 Pin HET[n] is not affected by the detection of an N2HET parity error.

1 Pin HET[n] is driven to a known state when an N2HET parity error is detected. The known state is a

function of bits HETDIR[n], HETPSL[n], HETPDR[n] as described in Table 23-45 (this state is also

independent of HETPULDIS[n]).

Table 23-45. Known State on Parity Error

HETDIR[n] HETPDR[n] HETPSL[n] Known State on Parity Error

0 x x High Impedance

1 0 0 Drive Logic 0

1 0 1 Drive Logic 1

1 1 x High Impedance

Loading...

Loading...