ADC Registers

www.ti.com

944

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Analog To Digital Converter (ADC) Module

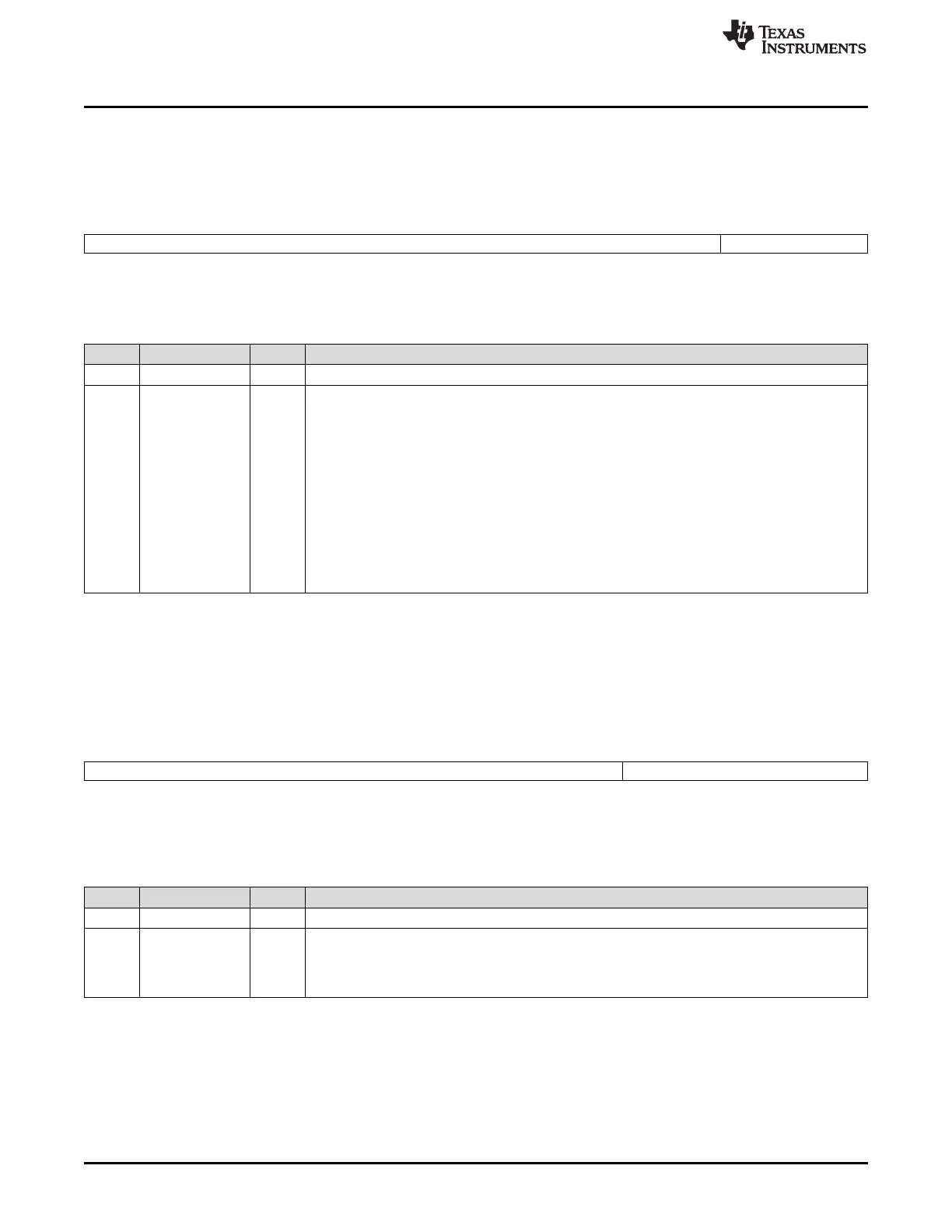

22.3.62 ADC Group2 FIFO Reset Control Register (ADG2FIFORESETCR)

ADC Group2 FIFO Reset Control Register (ADG2FIFORESETCR) is shown in Figure 22-93 and

described in Table 22-68.

Figure 22-93. ADC Group2 FIFO Reset Control Register (ADG2FIFORESETCR) [offset = 170h]

31 1 0

Reserved G2_FIFO_RESET

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 22-68. ADC Group2 FIFO Reset Control Register (ADG2FIFORESETCR) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reads return 0. Writes have no effect.

0 G2_FIFO_RESET ADC Group2 FIFO Reset. The application can set this bit in case of an overrun condition. This

allows the ADC module to overwrite the contents of the Group2 results memory starting from the

first location.

When this bit is set to 1, the ADC module resets its internal Group2 results memory pointers. Then

this bit automatically gets cleared, so that the ADC module allows the Group2 results memory to be

overwritten only once each time this bit is set to 1. As a result, the G2_FIFO_RESET bit will always

be read as a 0.

The G2_FIFO_RESET bit will only have the desired effect when the Group2 results memory is in an

overrun condition. It must be used when the data already available in the results memory can be

discarded.

If the application needs the Group2 memory to always be overwritten with the latest available

conversion results, then the OVR_G2_RAM_IGN bit in the Group2 operating mode control register

(ADG2MODECR) needs to be set to 1.

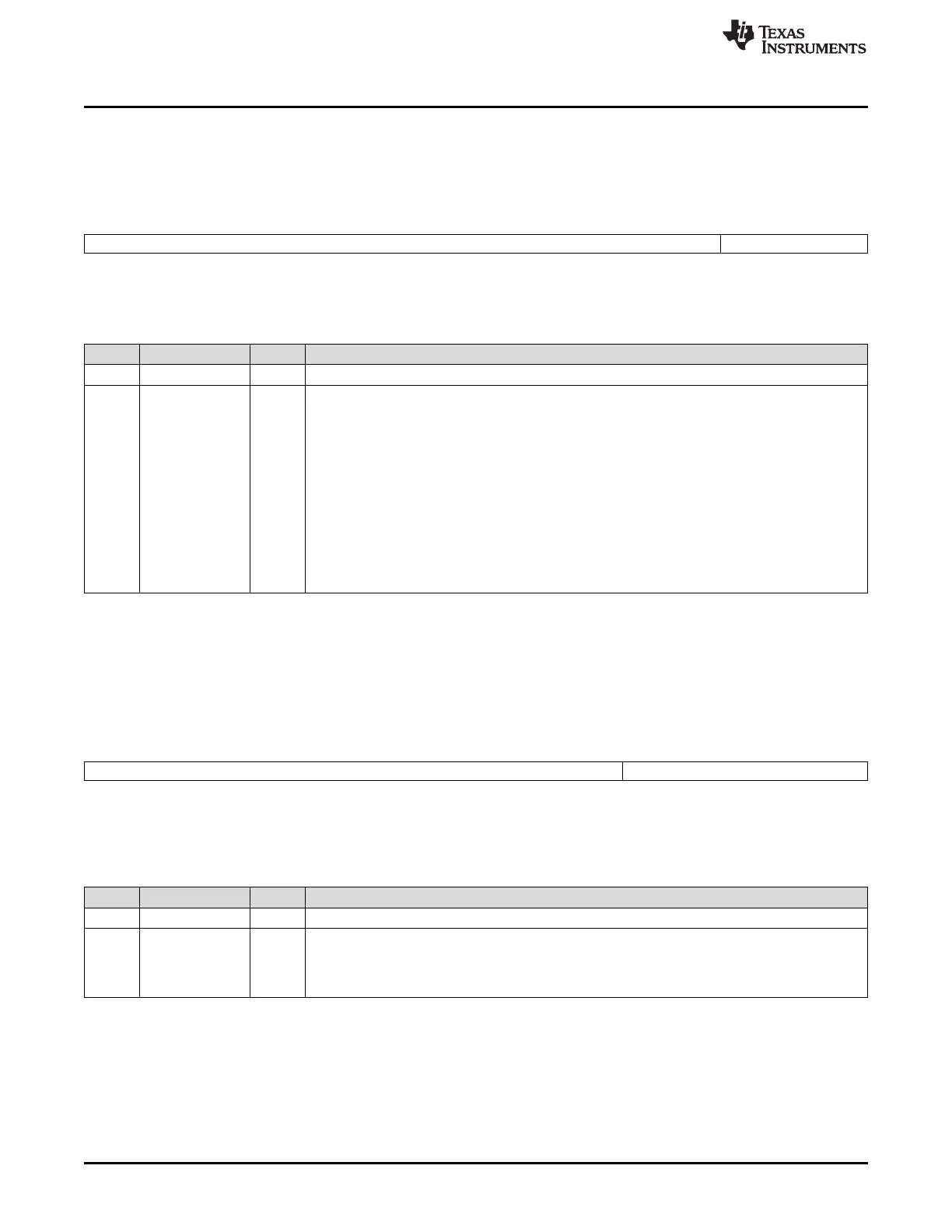

22.3.63 ADC Event Group RAM Write Address Register (ADEVRAMWRADDR)

ADC Event Group RAM Write Address Register (ADEVRAMWRADDR) is shown in Figure 22-94 and

described in Table 22-69.

Figure 22-94. ADC Event Group RAM Write Address Register (ADEVRAMWRADDR) [offset = 174h]

31 9 8 0

Reserved EV_RAM_ADDR

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 22-69. ADC Event Group RAM Write Address Register (ADEVRAMWRADDR)

Field Descriptions

Bit Field Value Description

31-9 Reserved 0 Reads return 0. Writes have no effect.

8-0 EV_RAM_ADDR Event Group results memory write pointer. This field shows the address of the location where the

next Event Group conversion result will be stored. This is specified in terms of the buffer number.

The application can read this register to determine the number of valid Event Group conversion

results available until that time.

Loading...

Loading...