www.ti.com

HTU Control Registers

1159

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer Transfer Unit (HTU) Module

24.4.13 Interrupt Offset Register 1 (HTU INTOFF1)

This register is organized identically to the INTOFF0 register. The difference is that INTOFF1 reflects the

highest priority interrupt flag bit set in the BERINTFL, RLOSTFL, or BFINTFL flag registers with the

appropriate CPINTMAP bit set to 1.

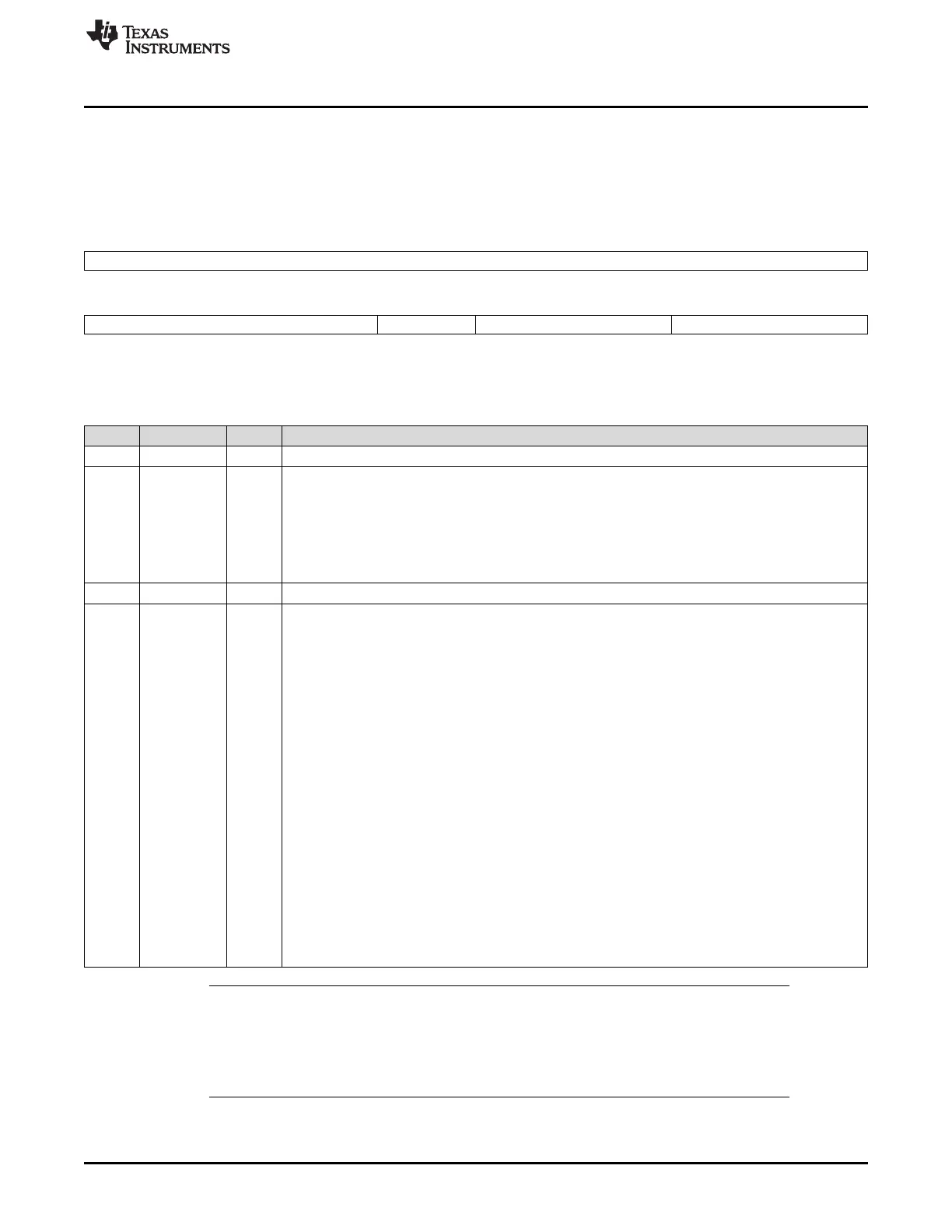

Figure 24-26. Interrupt Offset Register 1 (HTU INTOFF1) [offset = 38h]

31 16

Reserved

R-0

15 10 9 8 7 4 3 0

Reserved INTTYPE1 Reserved CPOFF1

R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

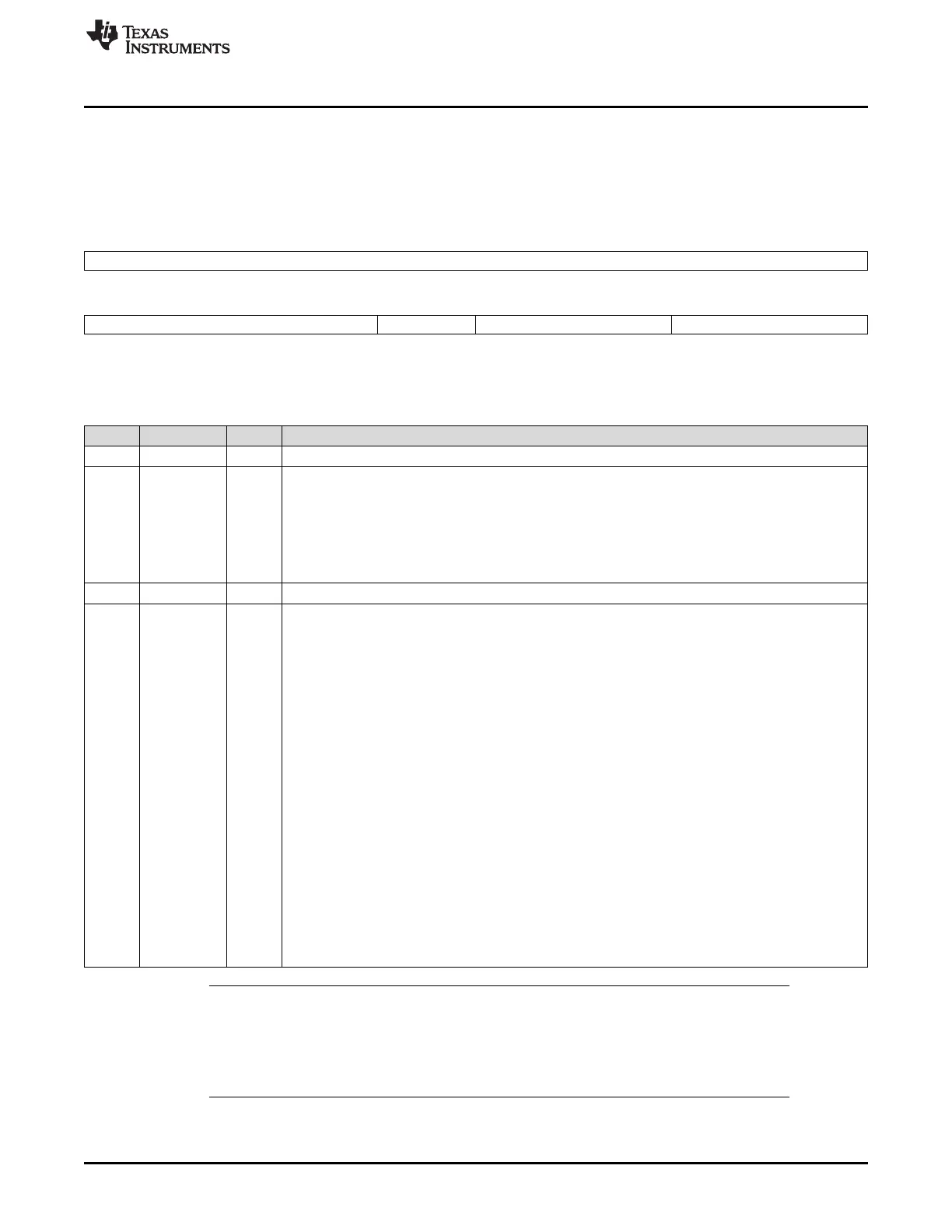

Table 24-25. Interrupt Offset Register 1 (HTU INTOFF1) Field Descriptions

Bit Field Value Description

31-10 Reserved 0 Reads return 0. Writes have no effect.

9-8 INTTYPE1 Interrupt Type of Interrupt Line 1. Indicates whether a buffer-full, RLOST, or BER interrupt, assigned to

interrupt line 1, is currently pending.

0 No interrupt.

1h Interrupt caused by full buffer on CP/DCP specified by CPOFF1.

2h RLOST interrupt generated by CP/DCP specified by CPOFF1.

3h BER interrupt generated by CP/DCP specified by bits CPOFF1.

7-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 CPOFF1 CP Offset. Indicates for which DCP / CP the interrupt is pending, which is classified by INTTYPE1 and

is assigned to interrupt line 1.

0 DCP 0, CP A

1h DCP 0, CP B

2h DCP 1, CP A

3h DCP 1, CP B

4h DCP 2, CP A

5h DCP 2, CP B

6h DCP 3, CP A

7h DCP 3, CP B

8h DCP 4, CP A

9h DCP 4, CP B

Ah DCP 5, CP A

Bh DCP 5, CP B

Ch DCP 6, CP A

Dh DCP 6, CP B

Eh DCP 7, CP A

Fh DCP 7, CP B

NOTE: Reading CPOFF1 will clear the bit generating the current interrupt from appropriate flag

register (BERINTFL, RLOSTFL, or BFINTFL), except when in debug mode where reading

CPOFF1 will have no effect on the flag registers.

In order to read INTTYPE1 and CPOFF1 simultaneously, always read this register using

word or half-word but not using byte accesses.

Loading...

Loading...