www.ti.com

VIM Control Registers

681

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Vectored Interrupt Manager (VIM) Module

19.9.1 Interrupt Vector Table ECC Status Register (ECCSTAT)

Figure 19-12 and Table 19-6 describe this register.

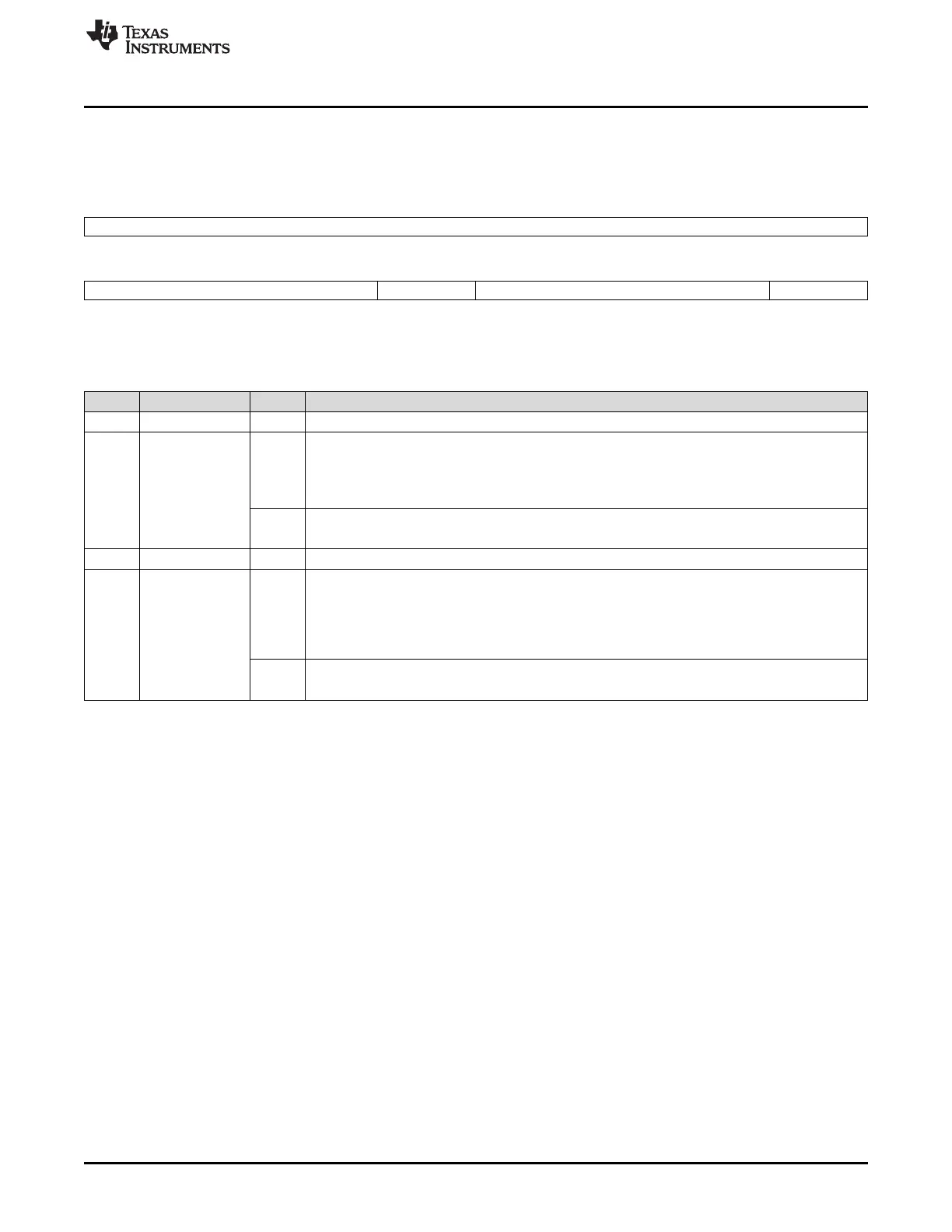

Figure 19-12. Interrupt Vector Table ECC Status Register (ECCSTAT) [offset = ECh]

31 16

Reserved

R-0

15 9 8 7 1 0

Reserved SBERR Reserved UERR

R-0 R/W1CP-0 R-0 R/W1CP-0

LEGEND: R/W = Read/Write; R = Read only; W1CP = Write 1 to clear in privilege mode only; -n = value after reset

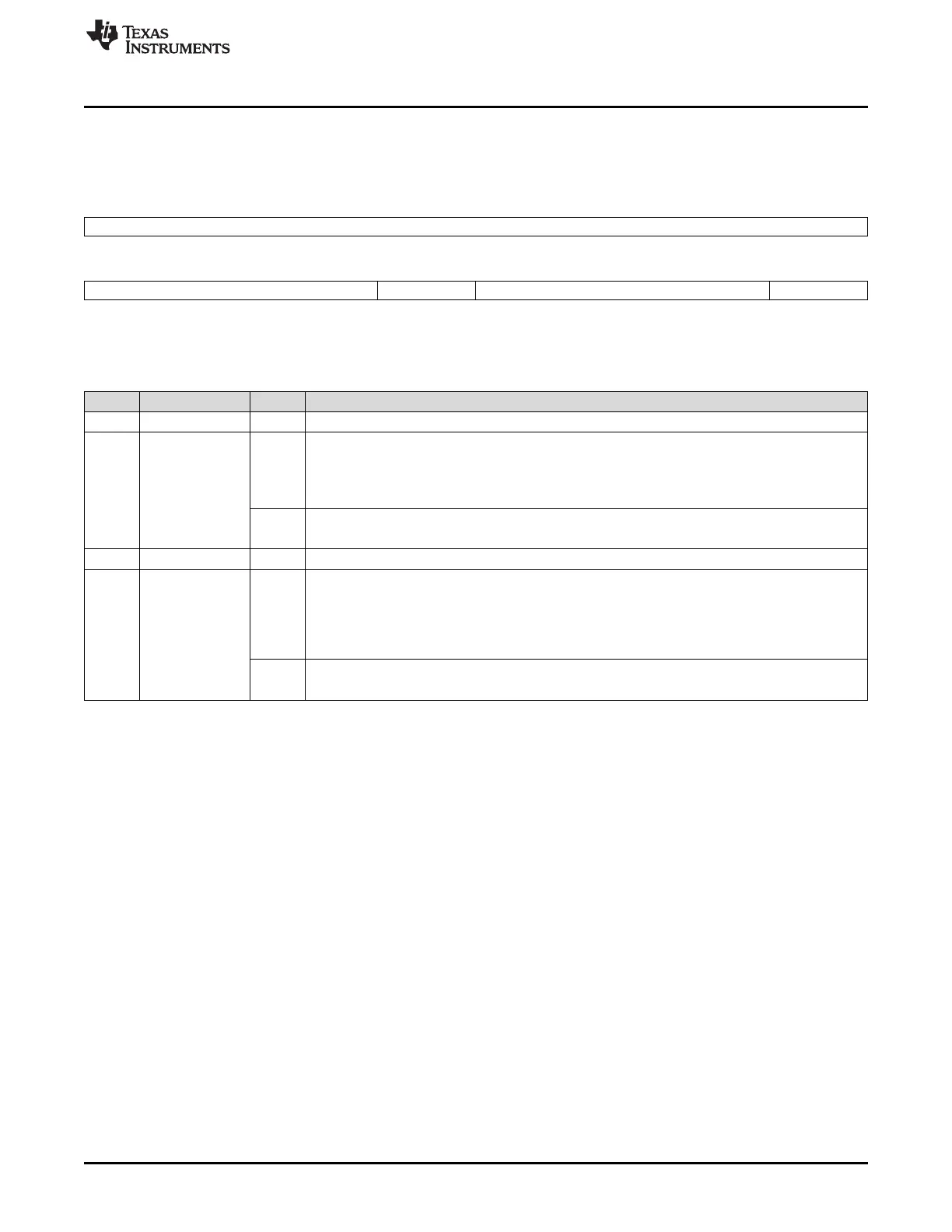

Table 19-6. Interrupt Vector Table ECC Status Register (ECCSTAT) Field Descriptions

Bit Field Value Description

31-9 Reserved 0 Reads return 0. Writes have no effect.

8 SBERR The SBERR indicates that a single-bit error has been detected and has been corrected by the

SECDED logic and the Interrupt Vector Table is being used for normal operation (not bypassed).

0 Read: No single-bit error has occurred.

Write: No effect.

1 Read: A single-bit error has occurred and was corrected by the SECDED logic.

Write: The SBERR bit is cleared.

7-1 Reserved 0 Reads return 0. Writes have no effect.

0 UERR The UERR indicates that a double-bit error has been found and that the Interrupt Vector Table is

bypassed. The resulting vector of any IRQ/FRQ interrupt is then the value contained in the

FBVECADDR register until this bit has been cleared.

0 Read: No double-bit error has occurred.

Write: No effect.

1 Read: A double-bit error has occurred and the Interrupt Vector Table is bypassed.

Write: The UERR bit is cleared and the interrupt vector can be read from the Interrupt Vector Table.

Loading...

Loading...