IOMM Registers

www.ti.com

332

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

I/O Multiplexing and Control Module (IOMM)

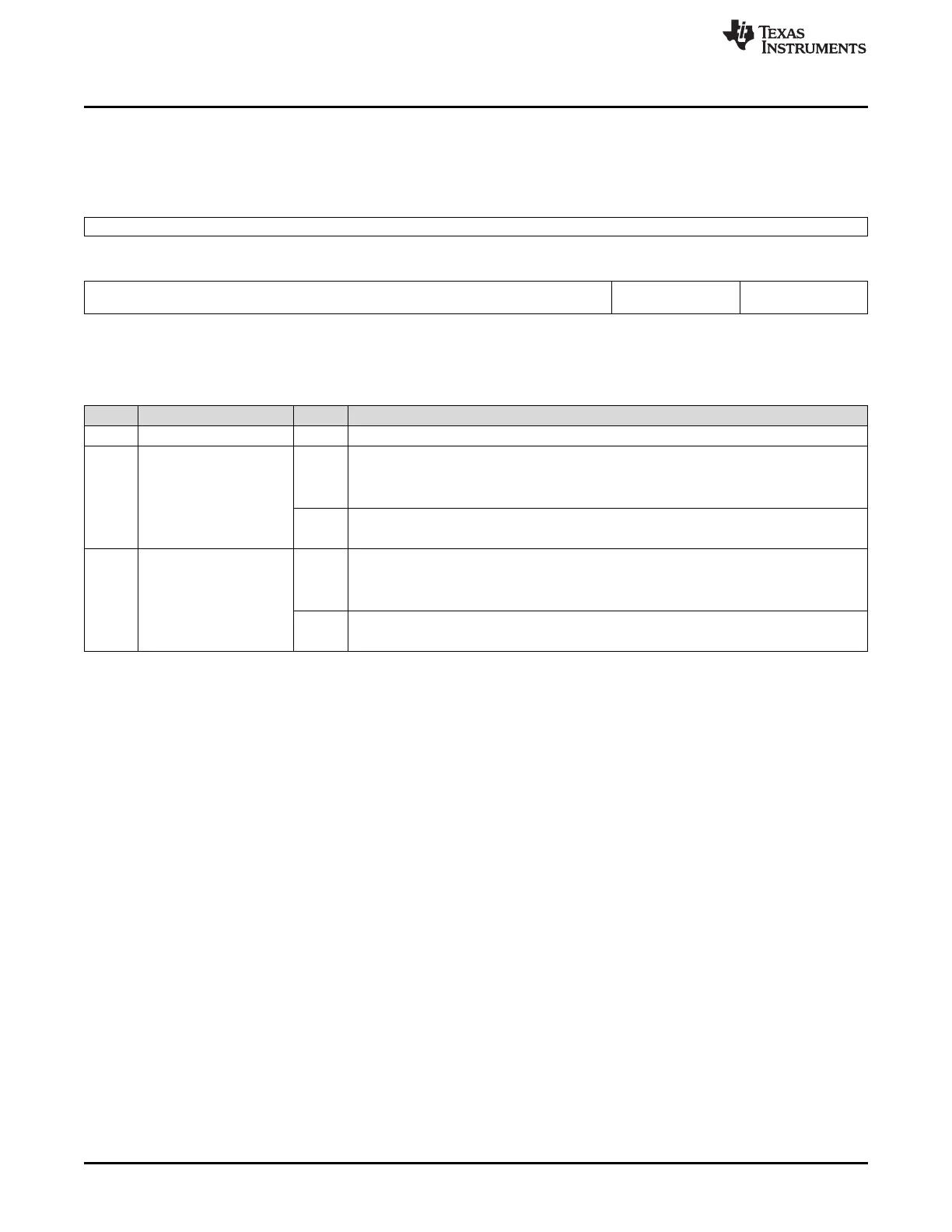

6.7.6 ERR_ENABLED_STATUS_REG: Error Enabled Status / Clear Register

This register shows the status of the error conditions and allows clearing of the error status.

Figure 6-15. ERR_ENABLED_STATUS_REG: Error Enabled Status / Clear Register (Offset = E4h)

31 8

Reserved

R-0

7 2 1 0

Reserved ENABLED_

ADDR_ERR

ENABLED_

PROT_ERR

R-0 R/WP-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

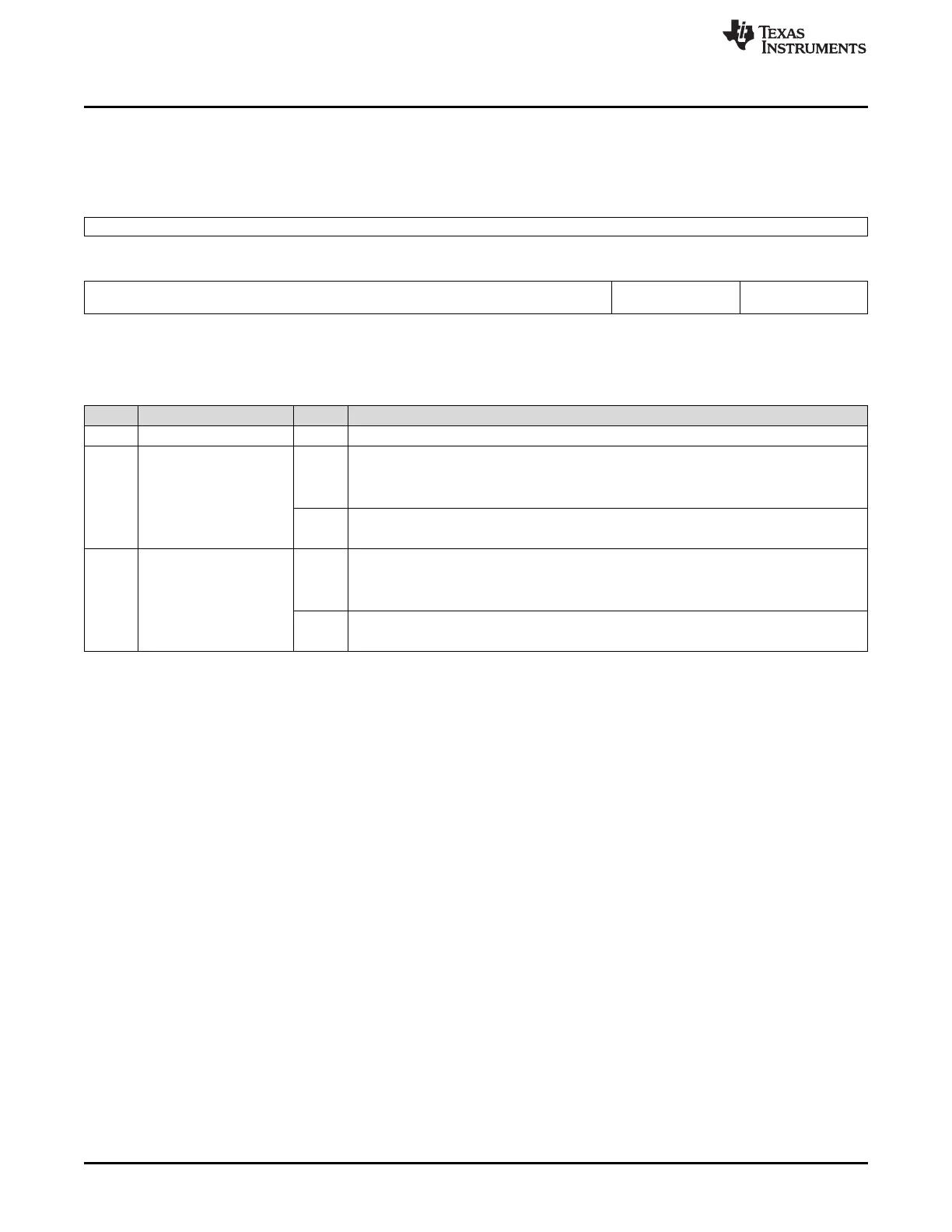

Table 6-18. Error Signaling Enabled Status / Clear Register Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reads return 0, writes have no effect.

1 ENABLED_ADDR_ERR Addressing Error Signaling Enable and Status Clear

0 Read: Addressing Error Signaling is disabled.

Write: Writing 0 has no effect.

1 Read: Addressing Error Signaling is enabled.

Write: Addressing Error status is cleared.

0 ENABLED_PROT_ERR Protection Error Signaling Enable and Status Clear

0 Read: Protection Error Signaling is disabled.

Write: Writing 0 has no effect.

1 Read: Protection Error Signaling is enabled.

Write: Protection Error status is cleared.

Loading...

Loading...