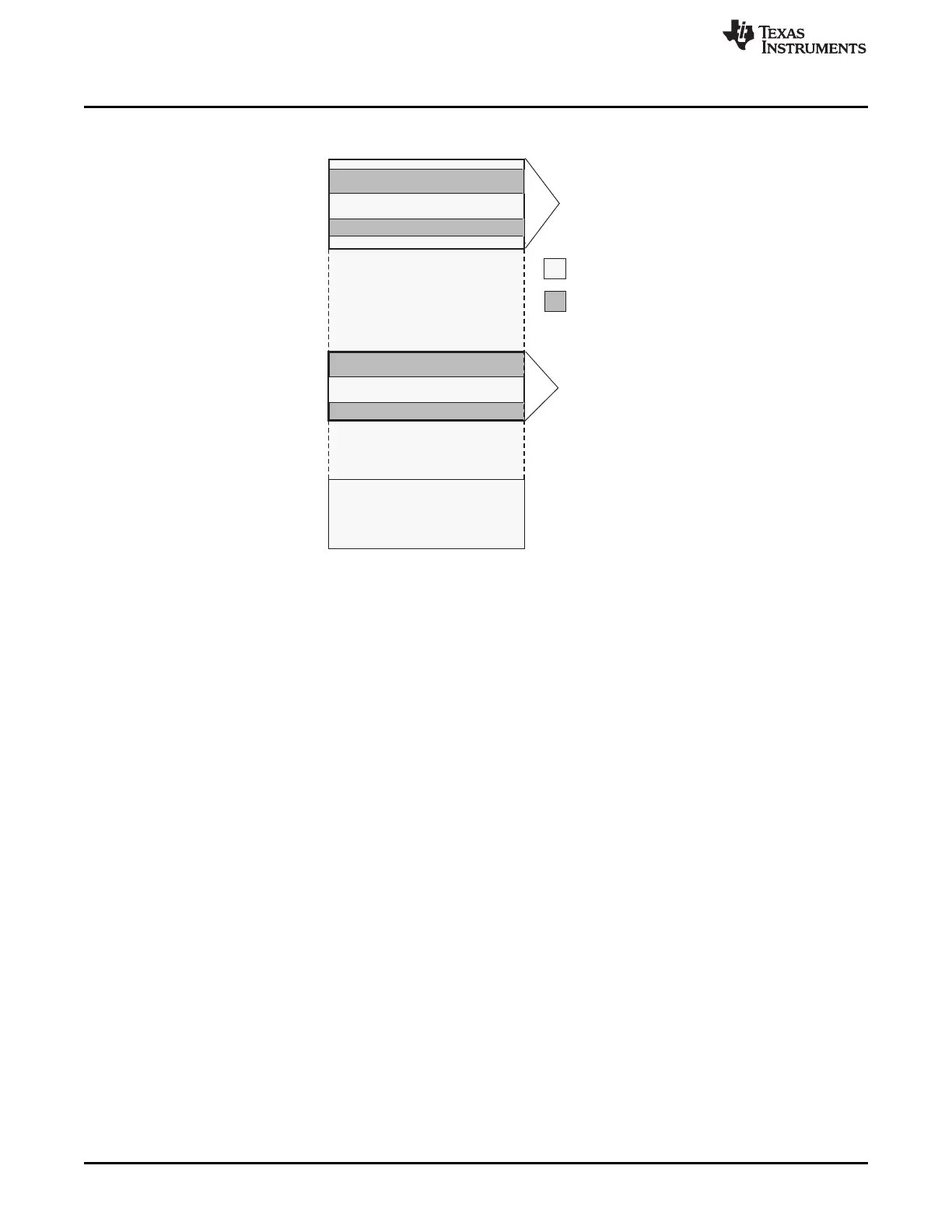

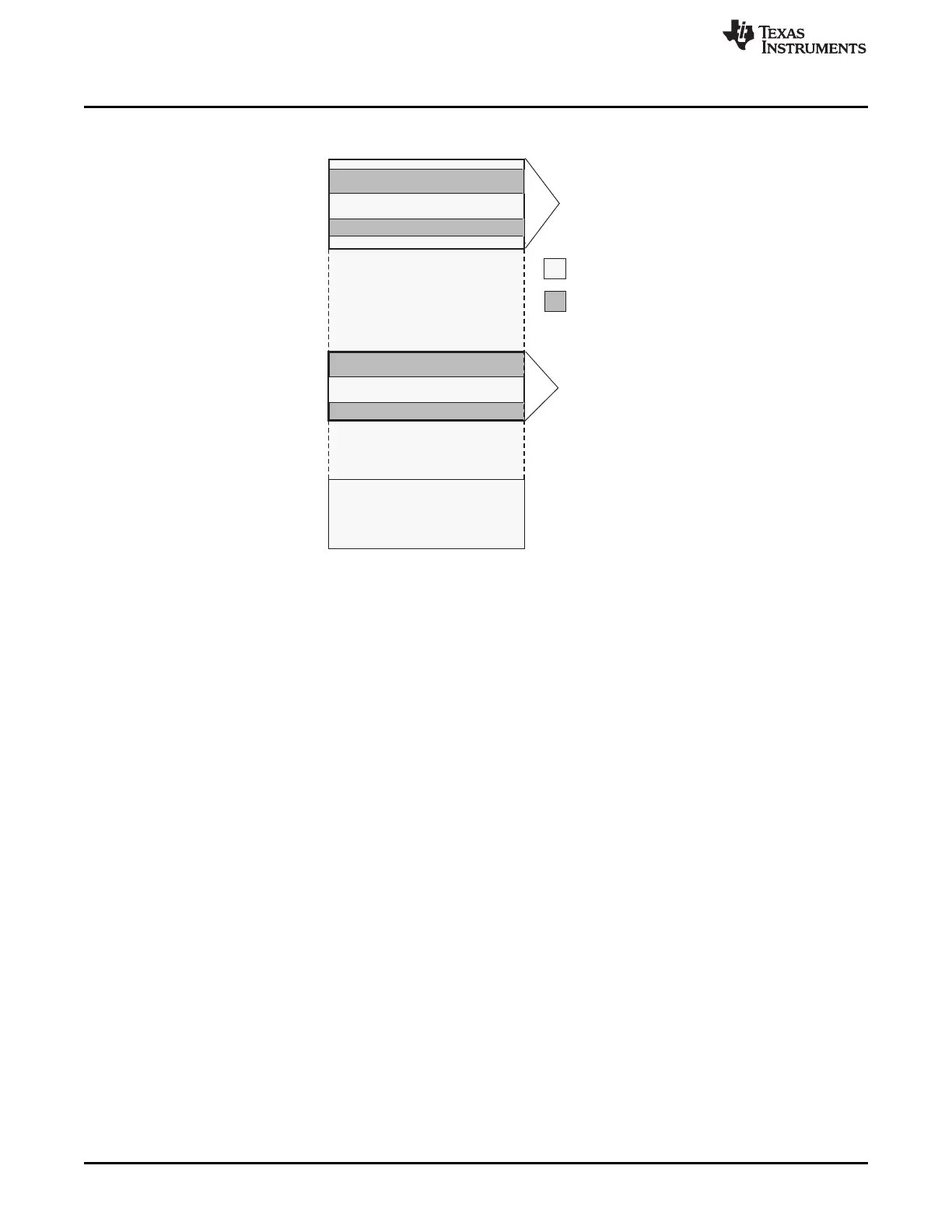

0x00000000

0x08000000

0x08003FFF

0xFFFFFFFF

System + peripherals

Region0

Region1

No access restrictions

Access restrictions

RAM

Region2

Region3

0xFFF78000

Module Operation

www.ti.com

718

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Direct Memory Access Controller (DMA) Module

Figure 20-17. Example of Protection Mechanism

20.2.16 ECC Checking

The Control packet RAM is protected using a Single Error Correction Double Error Detection (SECDED)

scheme. This scheme is implemented using a total of 9 ECC check bits for every 128 bits of data stored in

the DMA Control Packet RAM.

ECC checking can be enabled and disabled within the module by a 4-bit key. The key is located in the

ECC Control Register (Section 20.3.1.62).

During write accesses to Control Packet RAM, ECC bits are generated automatically and stored along

with the data bits to the memory.

During read accesses from the Control Packet RAM, the ECC bits in memory are checked against a

computed ECC value for the 128 bits of data. Following two kinds of errors can occur during the read:

• Single-Bit Error - If a single-bit error occurs during the reads to the control packet either by the CPU or

by DMA logic and the EDCAMODE[3:0] in DMASECCCTRL register is 0xA, the error is automatically

corrected. The SBEFLG bit in the register is also set to 1 to indicate a single-bit error was corrected.

The DMAECCSBE register is updated to indicate the error address. In addition, if the

SBE_EVT_EN[3:0] in DMASECCCTRL register is 0xA, the error is also indicated to ESM.

• Double-Bit Error - If a double-bit error occurs during the reads to the control packet either by the CPU

or the DMA logic and the ECC_ENA[3:0] in DMAPECR register is 0xA, the error is indicated to ESM.

The EDFLG bit gets set and the error address is stored in DMAPAR register.

The DMA module automatically performs read-modify-write operations to the Control Packet RAM which

are required during CPU configuration of the control packet RAM. Errors occuring during these reads are

also covered by the SECDED scheme. Also, reads to the Working Packet by CPU or DMA logic and

writes to the Working Packet by the DMA logic are also protected by SECDED.

During double-bit errors, it is possible to configure the behavior of the channel using the ERRA bit in

DMAPECR register. Two options are available:

• If ERRA bit is cleared, errors are ignored and channel operation will resume normally.

• If ERRA bit is set, errors will cause the DMA to be disabled (DMA_EN bit in GCTRL register is

cleared). All channels will stop servicing at the next arbitration boundary. This action will be taken

regardless of the origin of error being a CPU read or a DMA logic read.

Loading...

Loading...