EPC Control Registers

www.ti.com

490

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Error Profiling Controller (EPC)

12.4.2 EPC Control Register (EPCCNTRL)

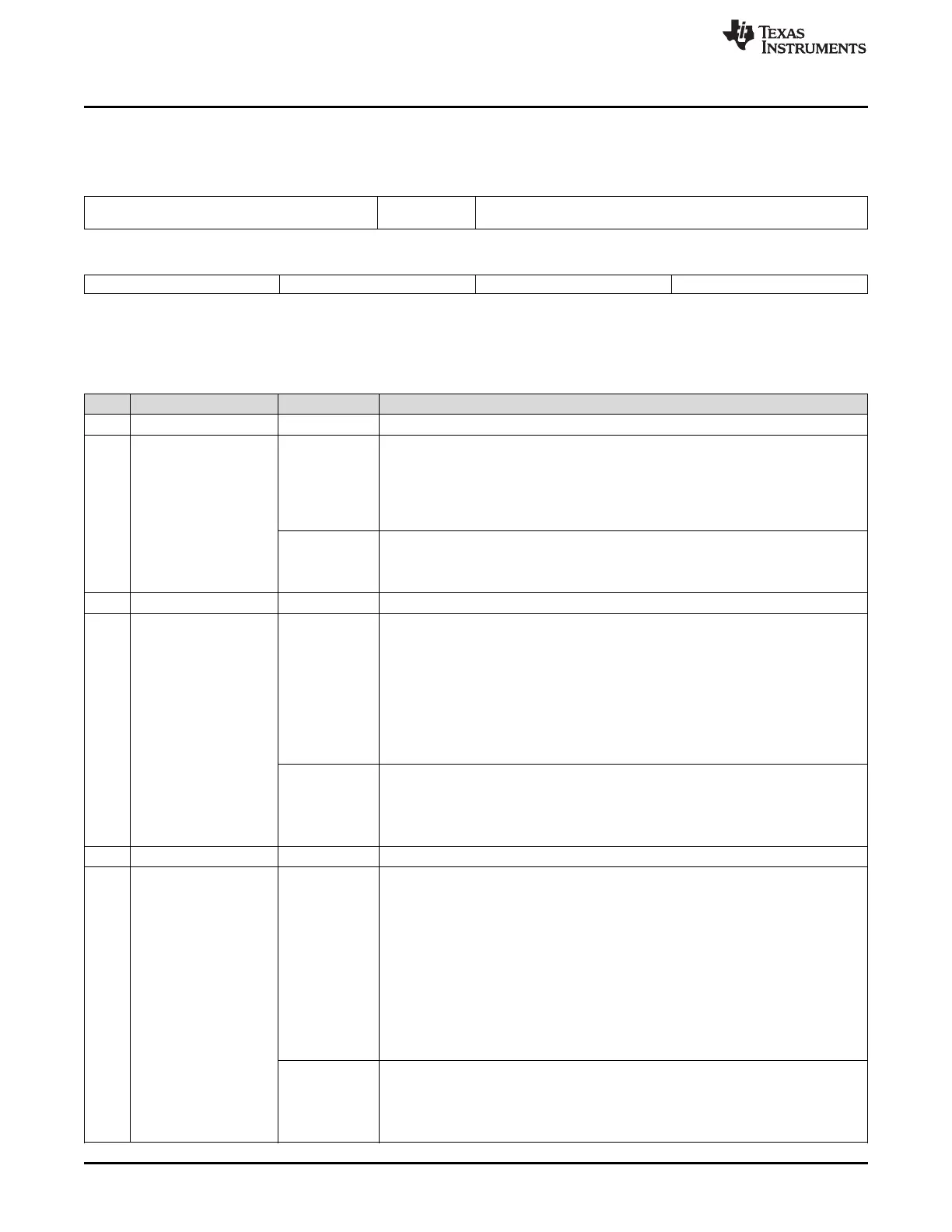

Figure 12-3. EPC Control Register (EPCCNTRL) (offset = 04h)

31 25 24 23 16

Reserved CAM/FIFO_

FULL_ENA

Reserved

R-0 R/WP-0 R-0

15 12 11 8 7 4 3 0

Reserved DIA_ENA_KEY Reserved SERRENA

R-0 R/WP-5h R-0 R/WP-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after synchronous reset on system reset

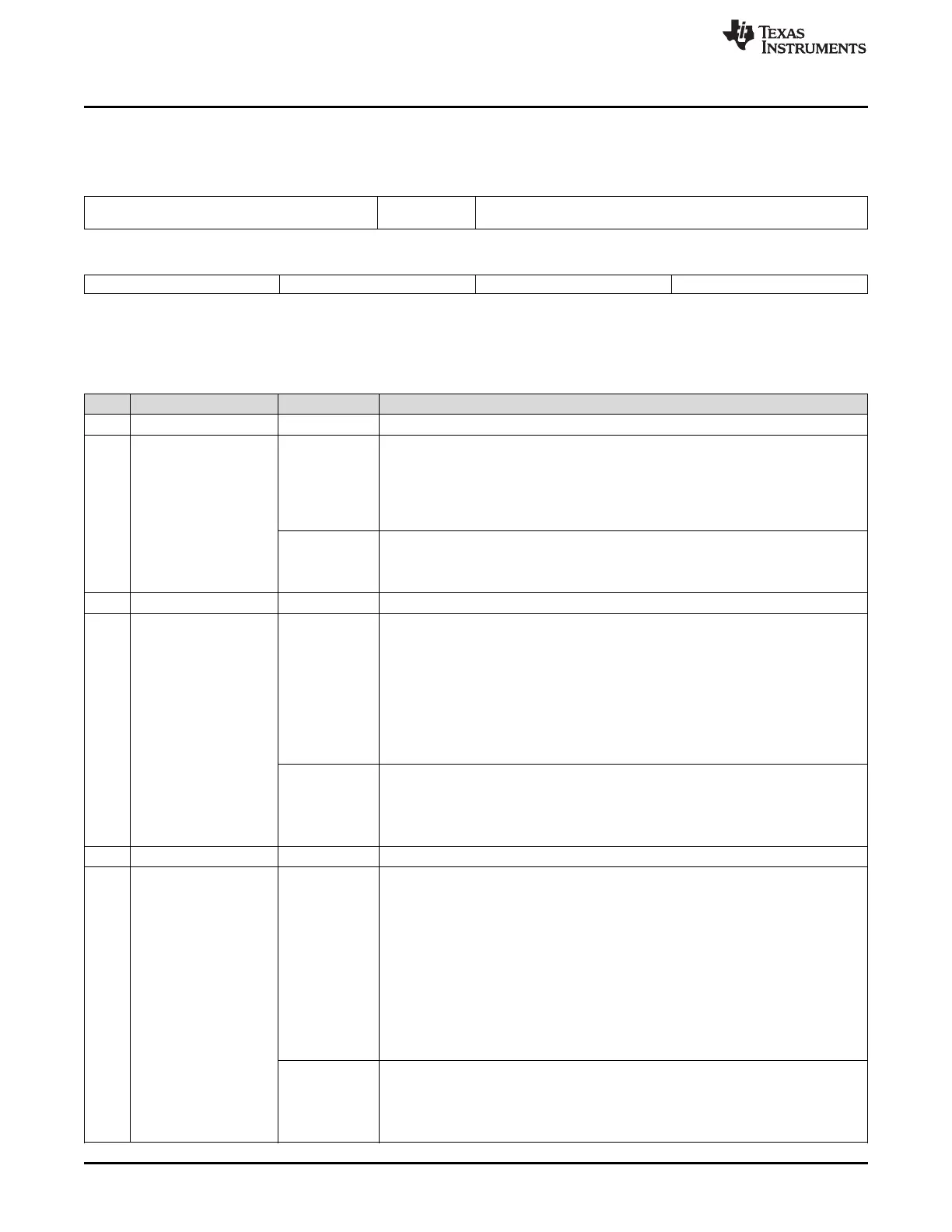

Table 12-3. EPC Control Register (EPCCNTRL) Field Descriptions

Bit Field Value Description

31-25 Reserved 0 Reserved. Reads return 0.

24 CAM/FIFO_FULL_ENA CAM or FIFO full interrupt enable. If this bit is set and CAM is full, CAM Full Interrupt

is generated.

Read:

0 CAM/FIFO full interrupt is disabled.

1 CAM/FIFO full interrupt is enabled.

Write in Privilege:

0 Disable CAM/FIFO full interrupt.

1 Enable CAM/FIFO full interrupt.

23-12 Reserved 0 Reserved. Reads return 0.

11-8 DIA_ENA_KEY CAM diagnostic enable key. These bits (when enabled) allow the CPU to access the

CAM content to clear or set any entry (CAM index) or write any pattern to CAM

content.

Internal RTL will implement self-correction logic to avoid single bit flipping.

Read:

5h CAM diagnostic is disabled.

Ah CAM diagnostic is enabled.

All other values Reserved

Write in Privilege:

5h CAM diagnostic is disabled.

Ah CAM diagnostic is enabled.

All other values Reserved

7-4 Reserved 0 Reserved. Reads return 0.

3-0 SERRENA Single (correctable) bit error event enable. These bits (when enable) cause EPC to

generate the serr_event if there is a correctable ECC fault address arrives from one of

the EPC-IP interface and the CAM has an empty entry. These bits also allow EPC to

generate the serr_event if there is a correctable ECC fault address arrives from one of

the EPC-IP interface and the CAM is full. In this case, CAM FULL status bit is set in

EPCERRSTAT.

Internal RTL will implement self-correction logic to avoid single bit flipping.

Read:

5h serr_event generation is disabled.

Ah serr_event generation is enabled.

All other values Reserved

Write in Privilege:

5h serr_event generation is disabled.

Ah serr_event generation is enabled.

All other values Reserved

Loading...

Loading...