www.ti.com

ESM Control Registers

567

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Error Signaling Module (ESM)

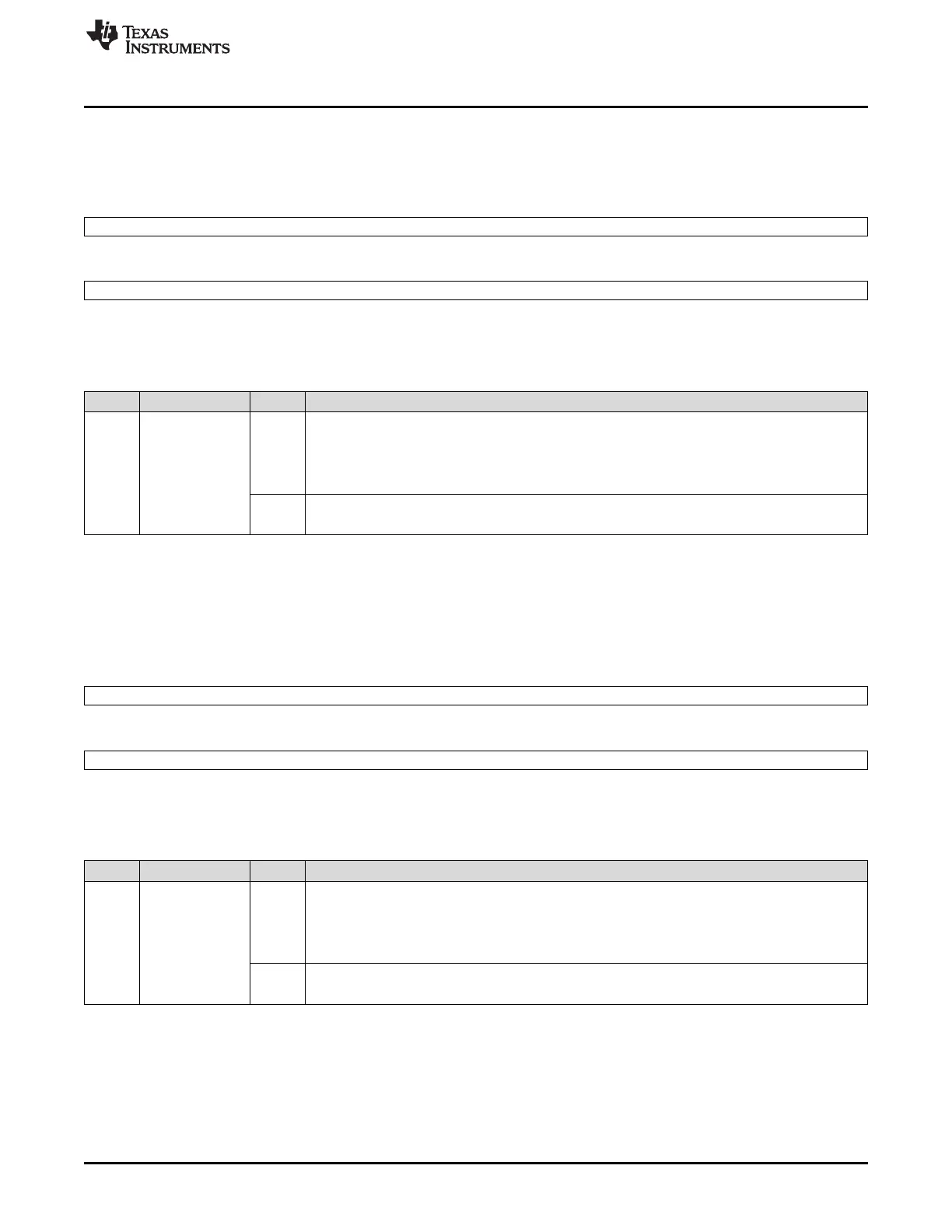

16.4.3 ESM Interrupt Enable Set/Status Register 1 (ESMIESR1)

This register is dedicated for Group1 Channel[31:0].

Figure 16-13. ESM Interrupt Enable Set/Status Register 1 (ESMIESR1) [offset = 08h]

31 16

INTENSET[31:16]

R/WP-0

15 0

INTENSET[15:0]

R/WP-0

LEGEND: R/W = Read/Write; WP = Write in privileged mode only; -n = value after reset

Table 16-5. ESM Interrupt Enable Set/Status Register 1 (ESMIESR1) Field Descriptions

Bit Field Value Description

31-0 INTENSET Set interrupt enable.

Read in User and Privileged mode. Write in Privileged mode only.

0 Read: Interrupt is disabled.

Write: Leaves the bit and the corresponding clear bit in the ESMIECR1 register unchanged.

1 Read: Interrupt is enabled.

Write: Enables interrupt and sets the corresponding clear bit in the ESMIECR1 register.

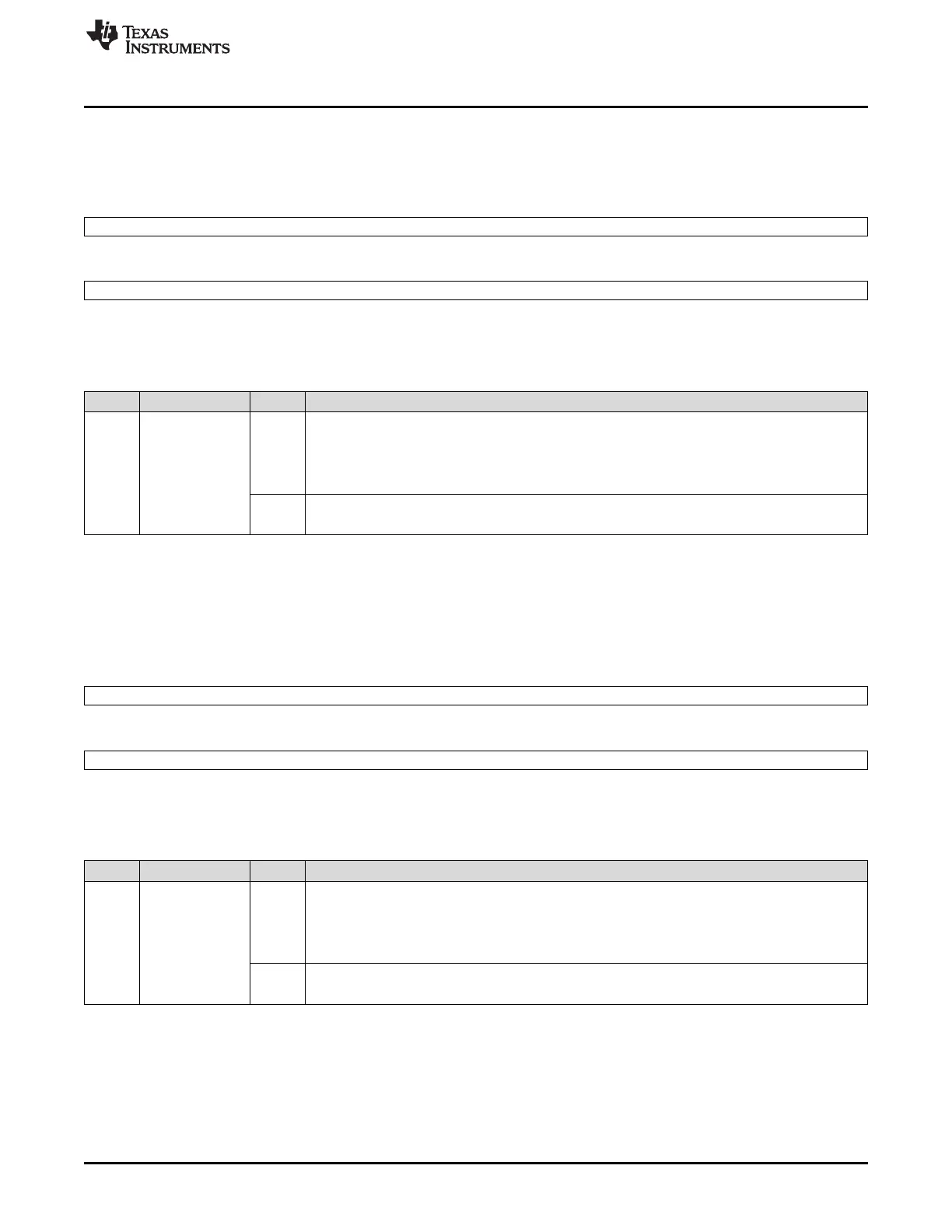

16.4.4 ESM Interrupt Enable Clear/Status Register 1 (ESMIECR1)

This register is dedicated for Group1 Channel[31:0].

Figure 16-14. ESM Interrupt Enable Clear/Status Register 1 (ESMIECR1) [offset = 0Ch]

31 16

INTENCLR[31:16]

R/WP-0

15 0

INTENCLR[15:0]

R/WP-0

LEGEND: R/W = Read/Write; WP = Write in privileged mode only; -n = value after reset

Table 16-6. ESM Interrupt Enable Clear/Status Register 1 (ESMIECR1) Field Descriptions

Bit Field Value Description

31-0 INTENCLR Clear interrupt enable.

Read in User and Privileged mode. Write in Privileged mode only.

0 Read: Interrupt is disabled.

Write: Leaves the bit and the corresponding set bit in the ESMIESR1 register unchanged.

1 Read: Interrupt is enabled.

Write: Disables interrupt and clears the corresponding set bit in the ESMIESR1 register.

Loading...

Loading...