N2HET Control Registers

www.ti.com

1024

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

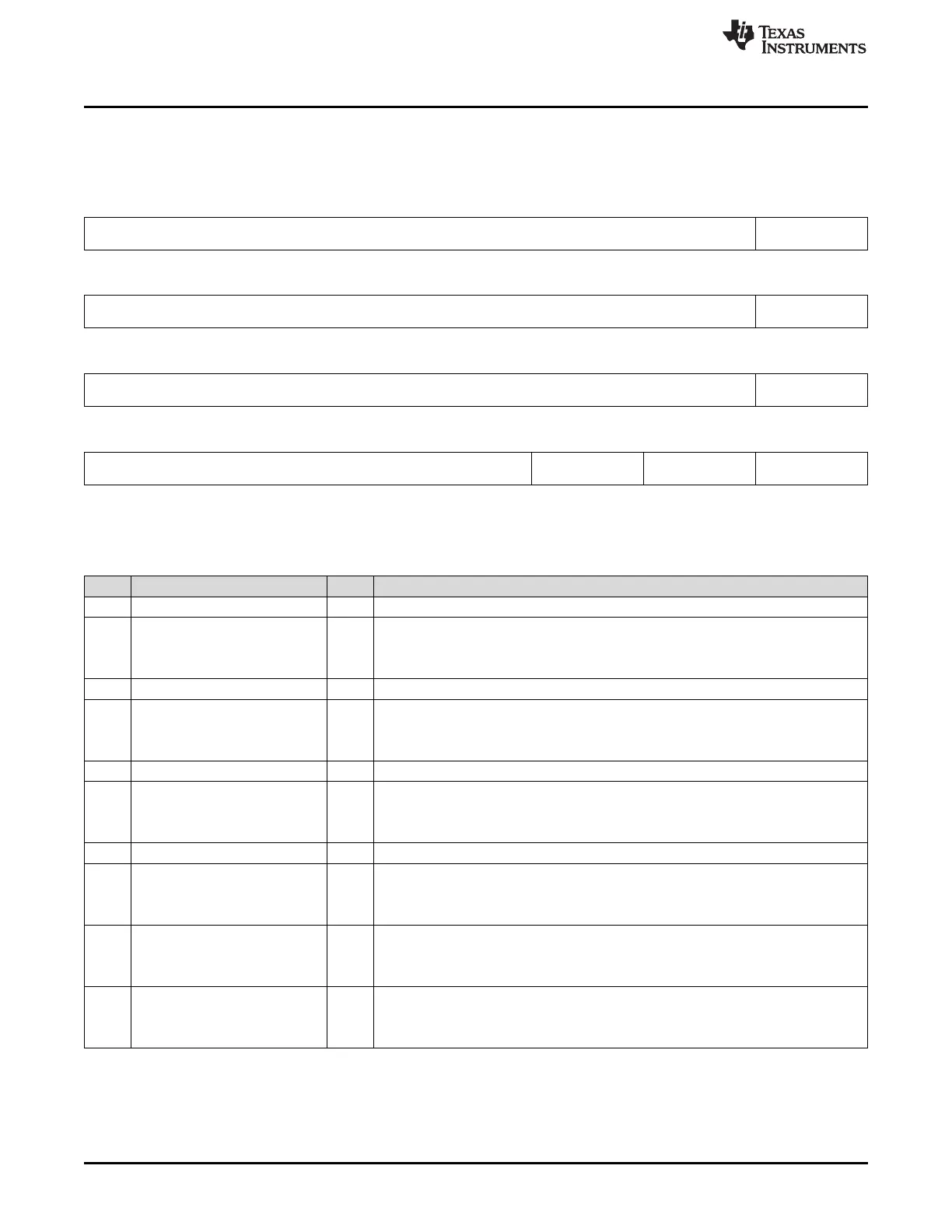

23.4.8 Exception Control Register 1 (HETEXC1)

N2HET1: offset = FFF7 B81Ch; N2HET2: offset = FFF7 B91Ch

Figure 23-63. Exception Control Register (HETEXC1)

31 25 24

Reserved APCNT_OVRFL_

ENA

R-0 R/W-0

23 17 16

Reserved APCNT_UNRFL_

ENA

R-0 R/W-0

15 9 8

Reserved PRGM_OVRFL_

ENA

R-0 R/W-0

7 3 2 1 0

Reserved APCNT_OVRFL_

PRY

APCNT_UNRFL_

PRY

PRGM_OVRFL_

PRY

R-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

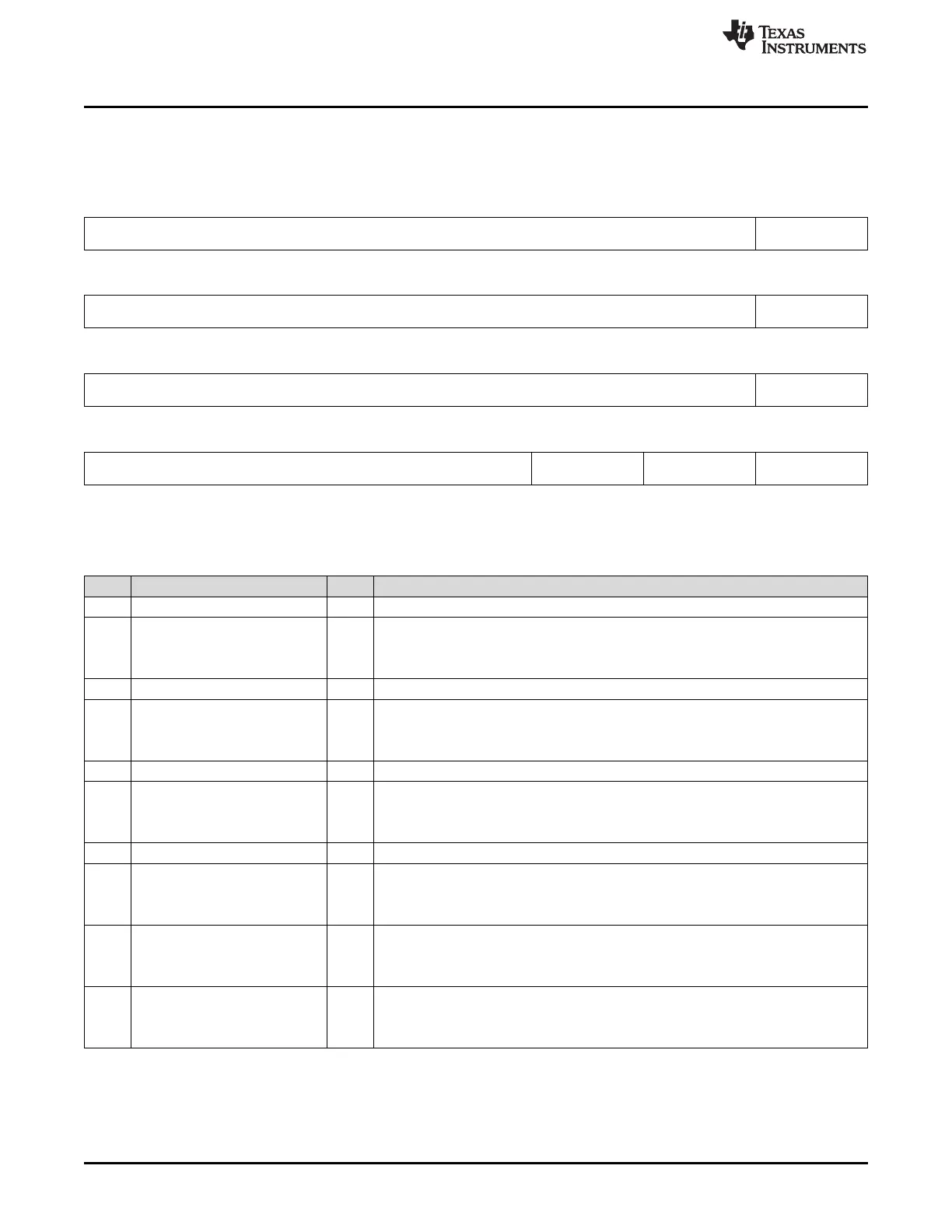

Table 23-24. Exception Control Register 1 (HETEXC1) Field Descriptions

Bit Field Value Description

31-17 Reserved 0 Reads return 0. Writes have no effect.

24 APCNT_OVRFL_ENA APCNT Overflow Enable

0 APCNT overflow exception is not enabled.

1 Enables the APCNT overflow exception.

23-17 Reserved 0 Reads return 0. Writes have no effect.

16 APCNT_UNRFL_ENA APCNT Underflow Enable

0 APCNT underflow exception is not enabled.

1 Enables the APCNT underflow exception.

15-9 Reserved 0 Reads return 0. Writes have no effect.

8 PRGM_OVRFL_ENA Program Overflow Enable

0 The program overflow exception is not enabled.

1 Enables the program overflow exception.

7-3 Reserved 0 Reads return 0. Writes have no effect.

2 APCNT_OVRFL_PRY APCNT Overflow Exception Interrupt Priority

0 Exception priority level 2.

1 Exception priority level 1.

1 APCNT_UNRFL_PRY APCNT Underflow Exception Interrupt Priority

0 Exception priority level 2.

1 Exception priority level 1.

0 PRGM_OVRFL_PRY ProgramOverflow Exception Interrupt Priority

0 Exception priority level 2.

1 Exception priority level 1.

Loading...

Loading...