IOMM Registers

www.ti.com

328

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

I/O Multiplexing and Control Module (IOMM)

6.7 IOMM Registers

Table 6-12 lists the control registers in the IOMM. The address offset is specified from the base address of

FFFF 1C00h.

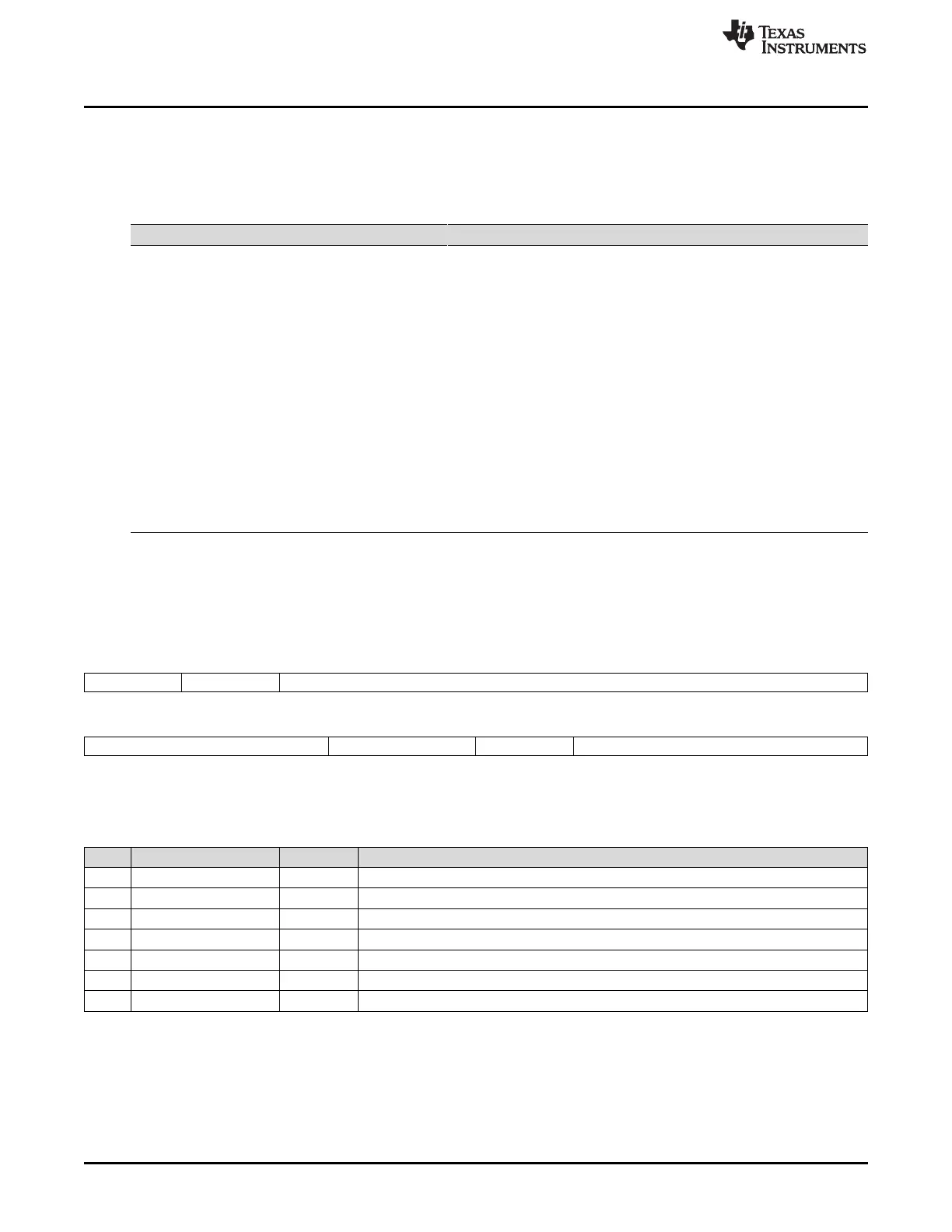

Table 6-12. IOMM Registers

Offset Acronym Register Description Section

00h REVISION_REG Revision Register Section 6.7.1

20h BOOT_REG Boot Mode Register Section 6.7.2

38h KICK_REG0 Kicker Register 0 Section 6.7.3

3Ch KICK_REG1 Kicker Register 1 Section 6.7.4

E0h ERR_RAW_STATUS_REG Error Raw Status / Set Register Section 6.7.5

E4h ERR_ENABLED_STATUS_REG Error Enabled Status / Clear Register Section 6.7.6

E8h ERR_ENABLE_REG Error Signaling Enable Register Section 6.7.7

ECh ERR_ENABLE_CLR_REG Error Signaling Enable Clear Register Section 6.7.8

F4h FAULT_ADDRESS_REG Fault Address Register Section 6.7.9

F8h FAULT_STATUS_REG Fault Status Register Section 6.7.10

FCh FAULT_CLEAR_REG Fault Clear Register Section 6.7.11

110h-1A4h PINMMRnn Output Pin Multiplexing Control Registers Section 6.7.12

250h-29Ch PINMMRnn Input Pin Multiplexing Control Registers Section 6.7.13

390h-3DCh PINMMRnn Special Functionality Control Registers Section 6.7.14

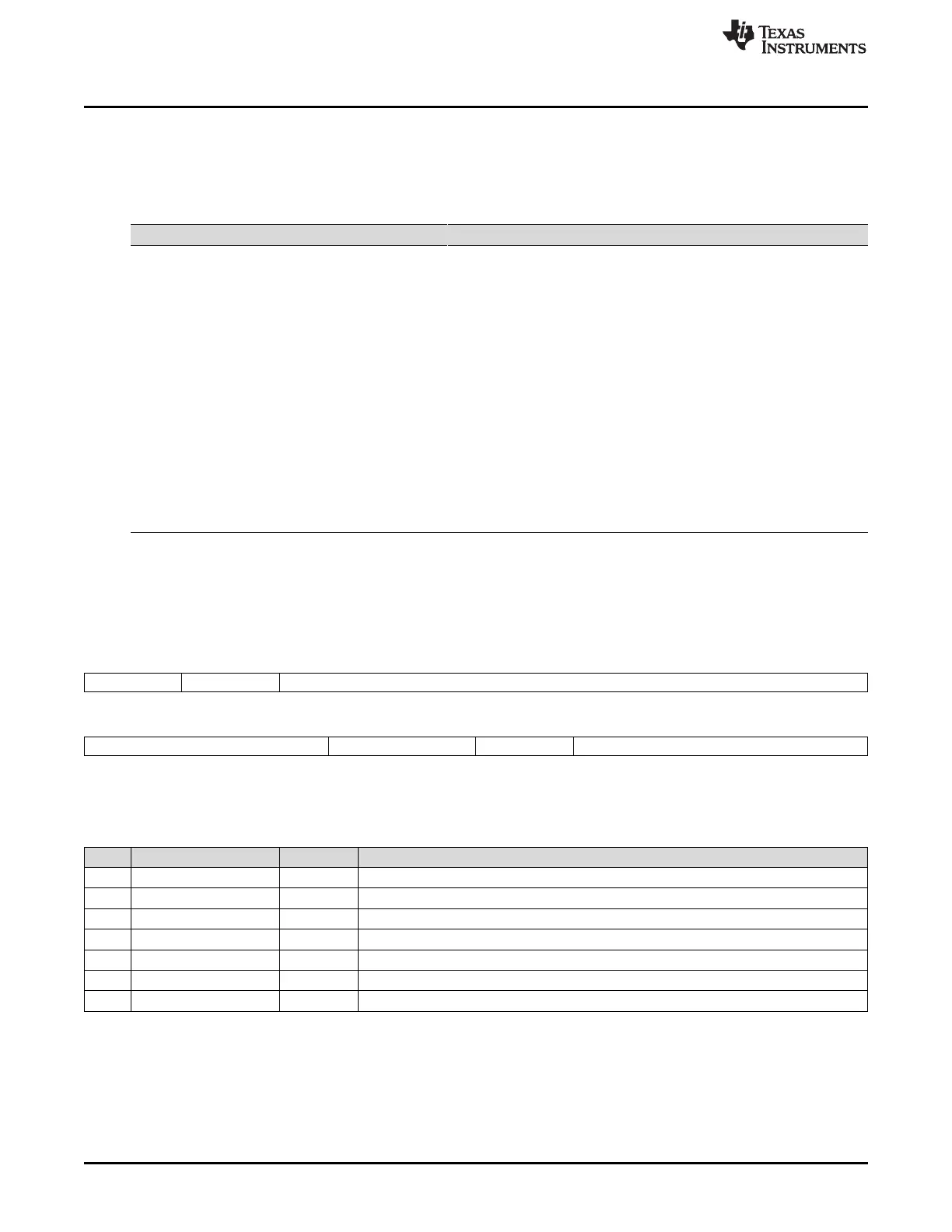

6.7.1 REVISION_REG: Revision Register

Figure 6-10. REVISION_REG: Revision Register (Offset = 00h)

31 30 29 28 27 16

REV SCHEME Reserved REV MODULE

R-1 R-0 R-E84h

15 11 10 8 7 6 5 0

REV RTL REV MAJOR REV CUSTOM REV MINOR

R-0 R-1 R-0 R-2h

LEGEND: R = Read only; C = Clear; -n = value after reset

Table 6-13. Revision Register Field Descriptions

Bit Field Value Description

31-30 REV SCHEME 01 Revision Scheme

29-28 Reserved 0 Reads return 0, writes have no effect.

27-16 REV MODULE E84h Module Id

15-11 REV RTL 0 RTL Revision

10-8 REV MAJOR 001 Major Revision

7-6 REV CUSTOM 0 Custom Revision

5-0 REV MINOR 2h Minor Revision

Loading...

Loading...