FIQ INDEX

INT_

REQ0

IRQ

FIQ

FIQ LEVEL

PRIORITY ENCODER

IRQ LEVEL

PRIORITY ENCODER

CHANNEL

MAPPING

INT_

REQ1

INT_

REQ2

INT_

REQ126

INT_

REQ125

CHAN0

INTERRUPT

ENABLE

CHAN1 CHAN2

CHAN126

CHAN125

INT_

CHAN0

IRQ / FIQ

LEVEL

INT_

CHAN1

INT_

CHAN2

CHAN126

INT_

CHAN125

FIQ_

CHAN0

FIQ_

CHAN1

FIQ_

CHAN2

FIQ_

CHAN126

FIQ_

CHAN125

IRQ_

CHAN2

IRQ_

CHAN126

IRQ_

CHAN125

IRQ INDEX

FIQ VECTOR

IRQ VECTOR

FIQVECREG

IRQVECREG

PROGRAMMABLE INTERRUPT VECTOR TABLE

Phantom Vector

Channel 0 Vector

Channel 1 Vector

Channel 126 Vector

FIQINDEX IRQINDEX

TO CPU

VIC Port

Register Register

To CPUTo CPU

Register Register

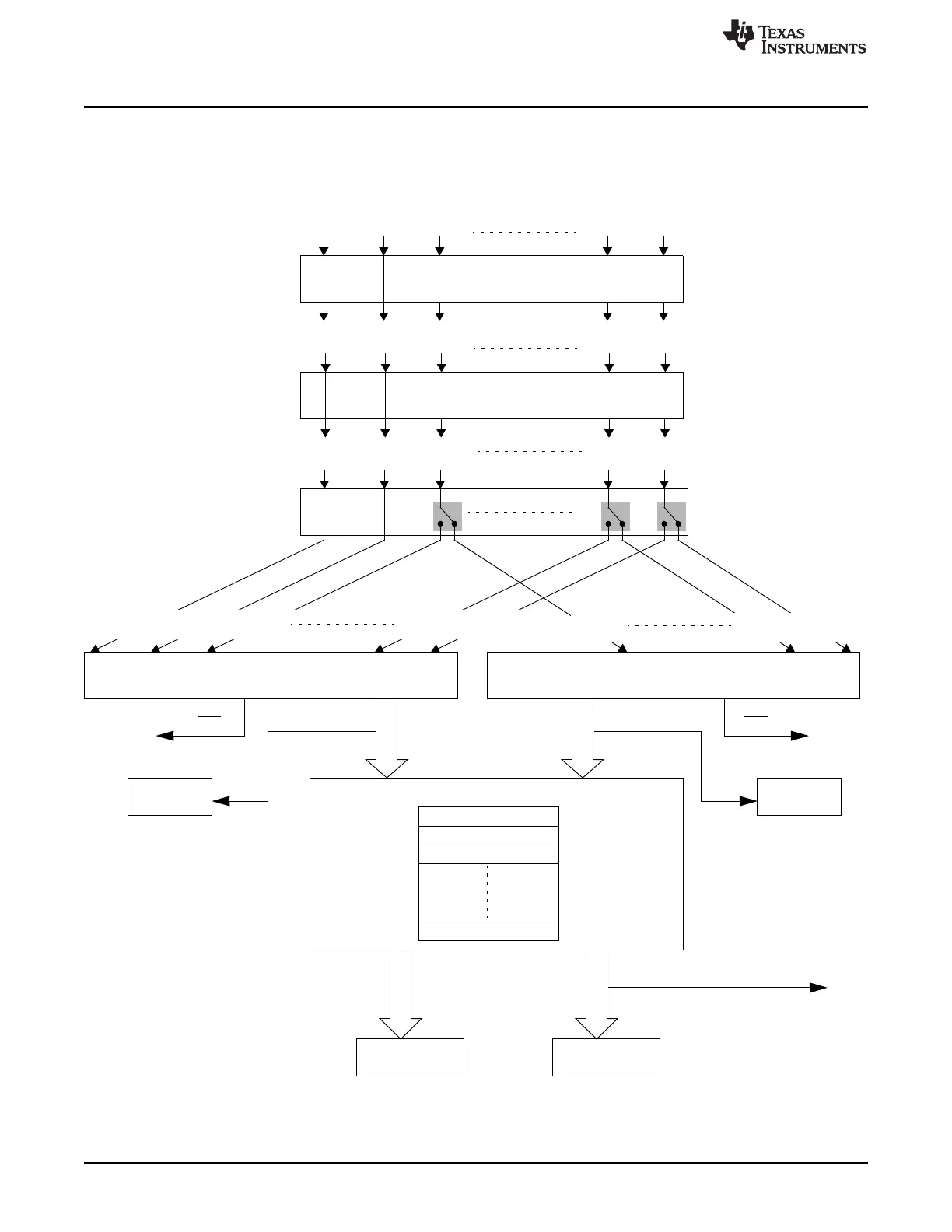

Interrupt Handling Inside VIM

www.ti.com

668

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Vectored Interrupt Manager (VIM) Module

19.4 Interrupt Handling Inside VIM

A block diagram of the interrupt handling inside VIM is shown in Figure 19-3

Figure 19-3. VIM Interrupt Handling Block Diagram

Loading...

Loading...