www.ti.com

Module Operation

637

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Cyclic Redundancy Check (CRC) Controller Module

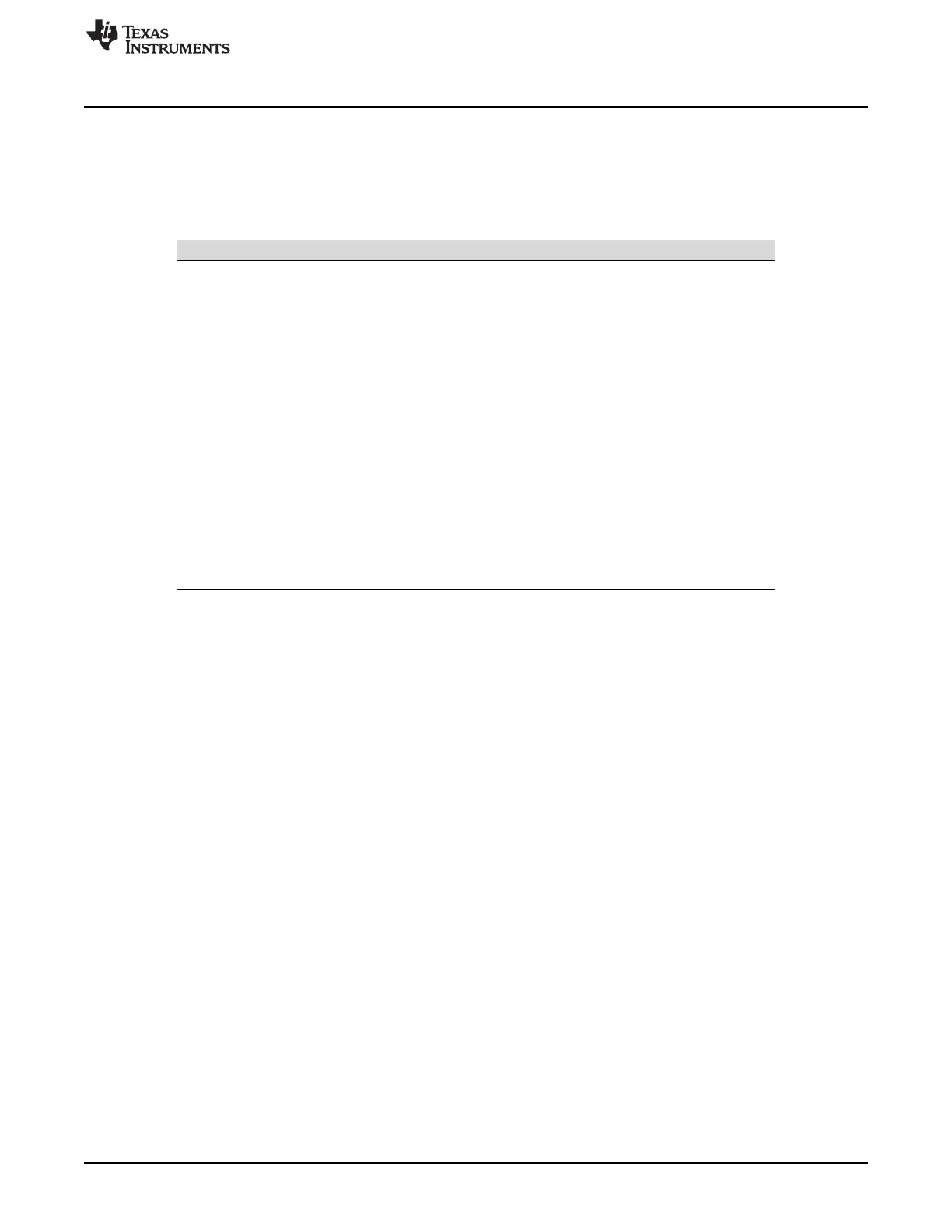

18.2.10.6 Interrupt Offset Register

CRC Controller only generates one interrupt request to interrupt manager. A interrupt offset register is

provided to indicate the source of the pending interrupt with highest priority. Table 18-3 shows the offset

interrupt vector address of each interrupt condition in an ascending order of priority.

Table 18-3. Interrupt Offset Mapping

Offset Value Interrupt Condition

0 Phantom

1h Ch1 CRC Fail

2h Ch2 CRC Fail

3h-8h Reserved

9h Ch1 Compression Complete

Ah Ch2 Compression Complete

Bh-10h Reserved

11h Ch1 Overrun

12h Ch2 Overrun

13h-18h Reserved

19h Ch1 Underrun

1Ah Ch2 Underrun

1Bh-20h Reserved

21h Ch1 Timeout

22h Ch2 Timeout

23h-24h Reserved

18.2.10.7 Error Handling

When an interrupt is generated, host CPU should take appropriate actions to identify the source of error

and restart the respective channel in DMA and CRC module. To restart a CRC channel, the user should

perform the following steps in the ISR:

1. Write to software reset bit in CRC_CTRL register to reset the respective PSA Signature Register.

2. Reset the CHx_MODE bits to 00 in CRC_CTRL register as Data capture mode.

3. Set the CHx_MODE bits in CRC_CTRL register to desired new mode again.

4. Release software reset.

The host CPU should use byte write to restart each individual channel.

18.2.11 Power Down Mode

CRC module can be put into power down mode when the power down control bit PWDN is set. The

module wakes up when the PWDN bit is cleared.

18.2.12 Emulation

A read access from a register in functional mode can sometimes trigger a certain internal event to follow.

For example, reading an interrupt offset register triggers an event to clear the corresponding interrupt

status flag. During emulation when SUSPEND signal is high, a read access from any register should only

return the register contents to the bus and should not trigger or mask any event as it would have in

functional mode. This is to prevent debugger from reading the interrupt offset register during refreshing

screen and cause the corresponding interrupt status flag to get cleared. Timeout counters are stopped to

generate timeout interrupts in emulation mode. No Peripheral Master bus error should be generated if

reading from the unimplemented locations.

Loading...

Loading...