STC Control Registers

www.ti.com

452

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Self-Test Controller (STC) Module

10.8.7 Self-Test Fail Status Register (STCFSTAT)

This register is described in Figure 10-14 and Table 10-15.

NOTE: The three status bits can be cleared to their default values on a write of 1 to the bits.

Additionally when the STC_ENA key in STCGCR1 is written from a disabled state to an

enabled state, the three status bits get cleared to their default values. This register gets reset

to its default value with power-on reset assertion.

When multiple segments are enabled in a self-test run, the STC will indicate the self-test

complete on the first failed interval corresponding to a segment. The subsequent segments

will not be run. FSEG_ID bits in this register indicate which segment failed.

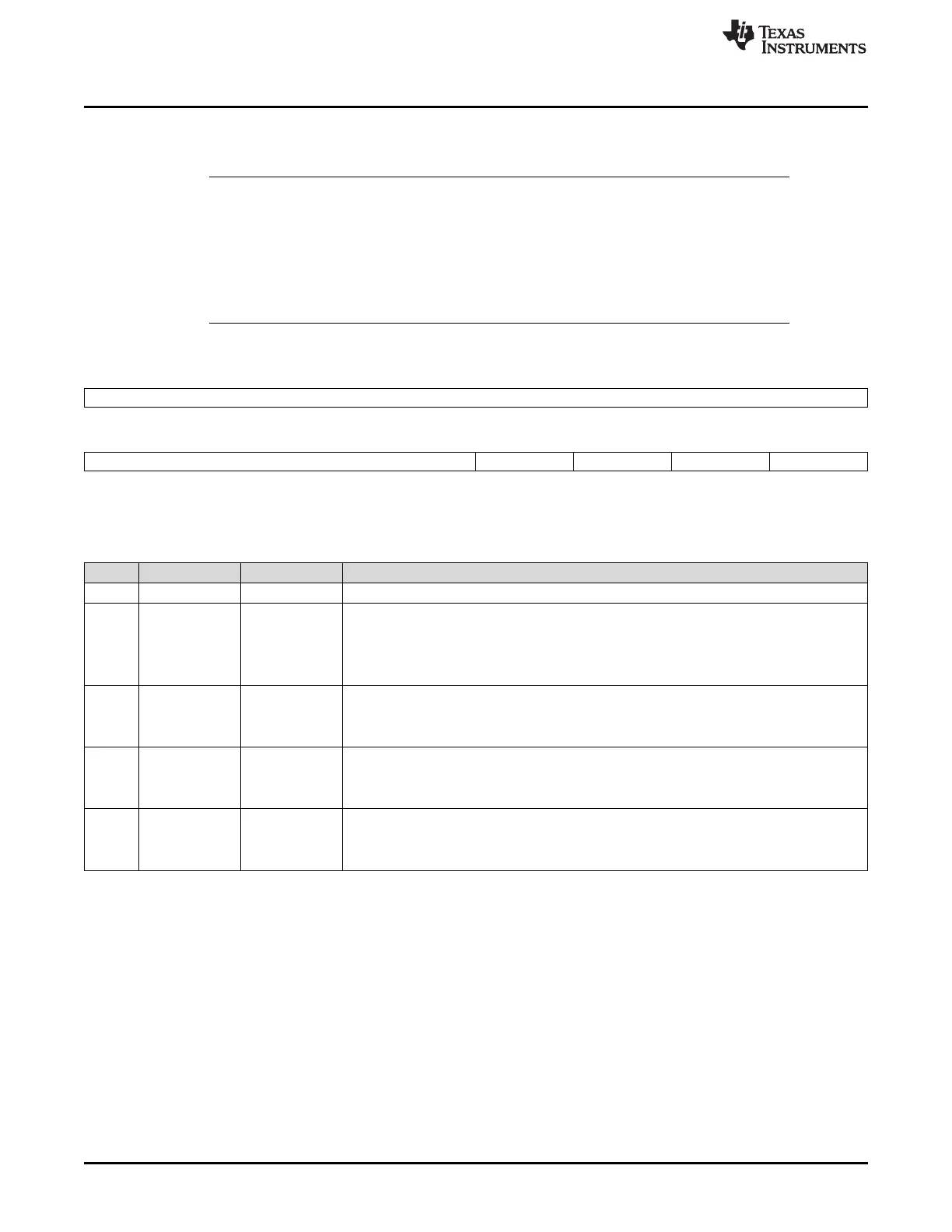

Figure 10-14. Self-Test Fail Status Register (STCFSTAT) [offset = 18h]

31 16

Reserved

R-0

15 5 4 3 2 1 0

Reserved FSEG_ID TO_ERR CORE2_FAIL CORE1_FAIL

R-0 RCP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0

LEGEND: R/W = Read/Write; R = Read only; W1CP = Write 1 to clear in privilege mode; -n = value after reset

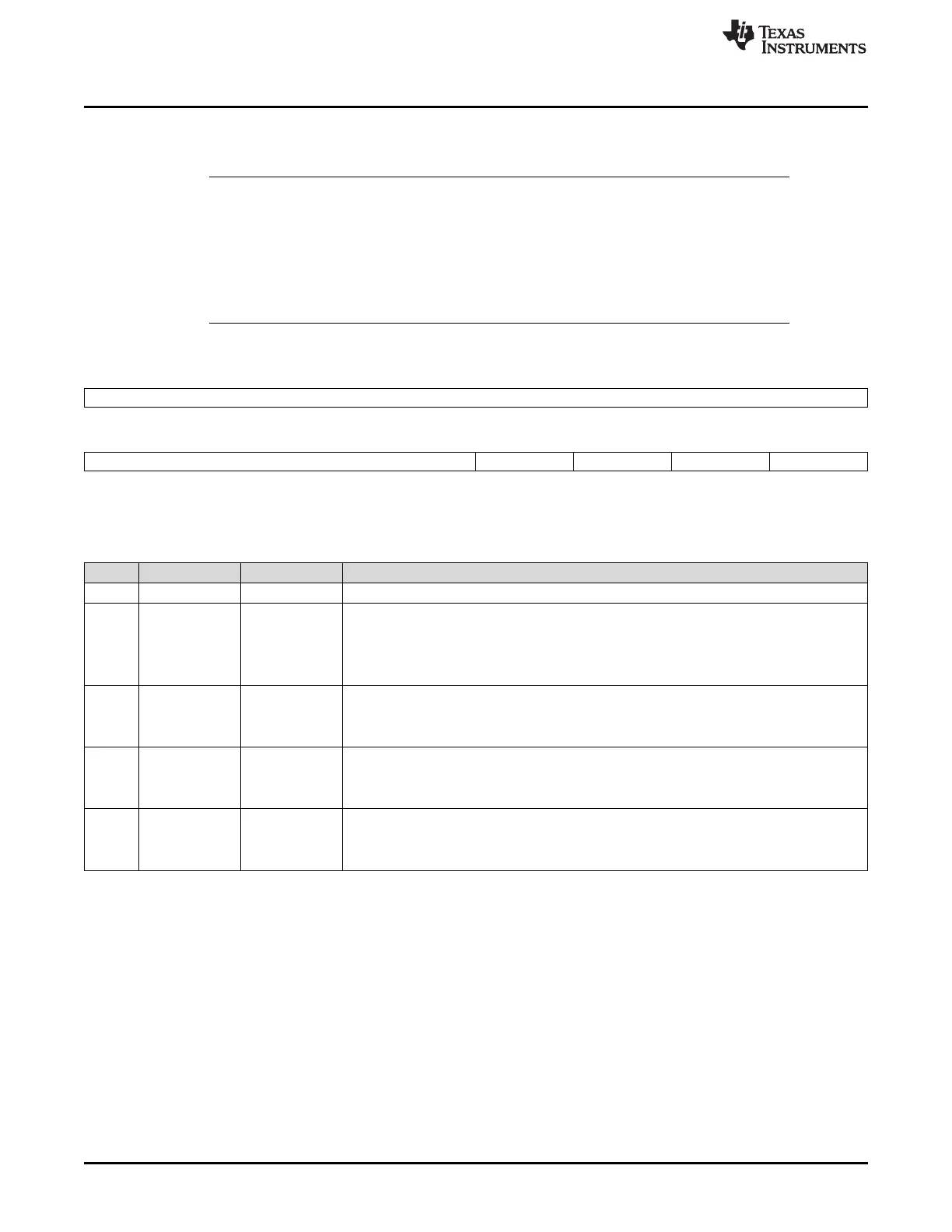

Table 10-15. Self-Test Fail Status Register (STCFSTAT) Field Descriptions

Bit Field Value Description

31-5 Reserved 0 Reads return 0. Writes have no effect.

4-3 FSEG_ID Failed Segment Number

0 Segment 0 Failed

1 Segment 1 Failed

All other values Reserved

2 TO_ERR Timeout Error

0 No time out error occurred.

1 Self-test run failed due to a timeout error.

1 CORE2_FAIL CORE2 failure info for segment 0 only.

0 No MISR mismatch for CORE2.

1 Self-test run failed due to MISR mismatch for CORE2.

0 CORE1_FAIL CORE1 failure info for segment 0 only.

0 No MISR mismatch for CORE1.

1 Self-test run failed due to MISR mismatch for CORE1.

Loading...

Loading...