Flash Control Registers

www.ti.com

374

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

F021 Level 2 Flash Module Controller (L2FMC)

7.10.23 Diagnostic Control Register (FDIAGCTRL)

First set the DIAGMODE and the DIAG_EN_KEY bits before setting up the other registers to block the

other registers from causing a false error. The final write should set the DIAG_TRIG bit to activate the test.

Running out of RAM will prevent problems with the diagnostic test corrupting the Flash access in some of

the modes.

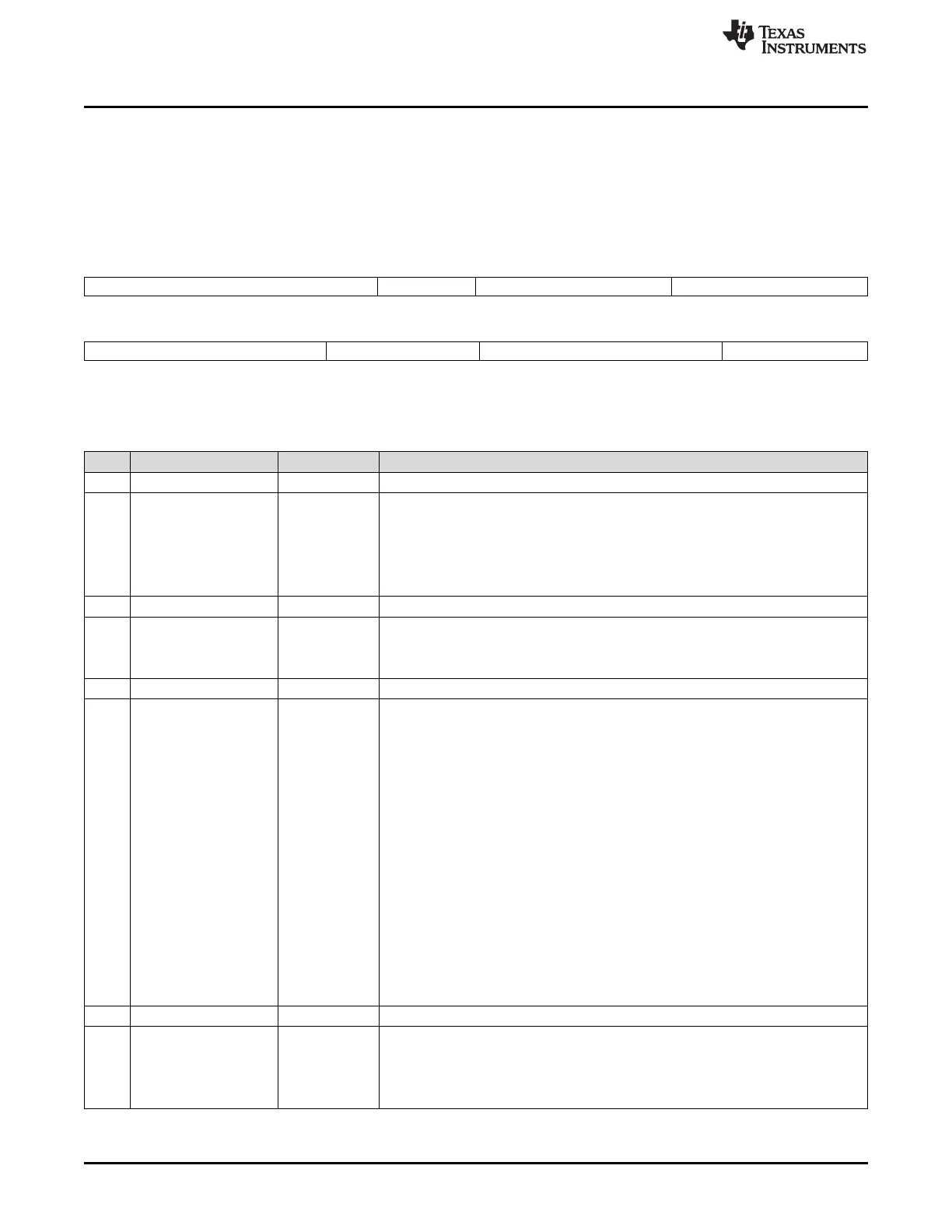

Figure 7-33. Diagnostic Control Register (FDIAGCTRL) (offset = 6Ch)

31 25 24 23 20 19 16

Reserved DIAG_TRIG Reserved DIAG_EN_KEY

R-0 R/WP-0 R-0 R/WP-Ah

15 11 10 8 7 3 2 0

Reserved DIAG_BUF_SEL Reserved DIAGMODE

R-0 R/WP-0 R-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in Privilege mode; -n = value after reset

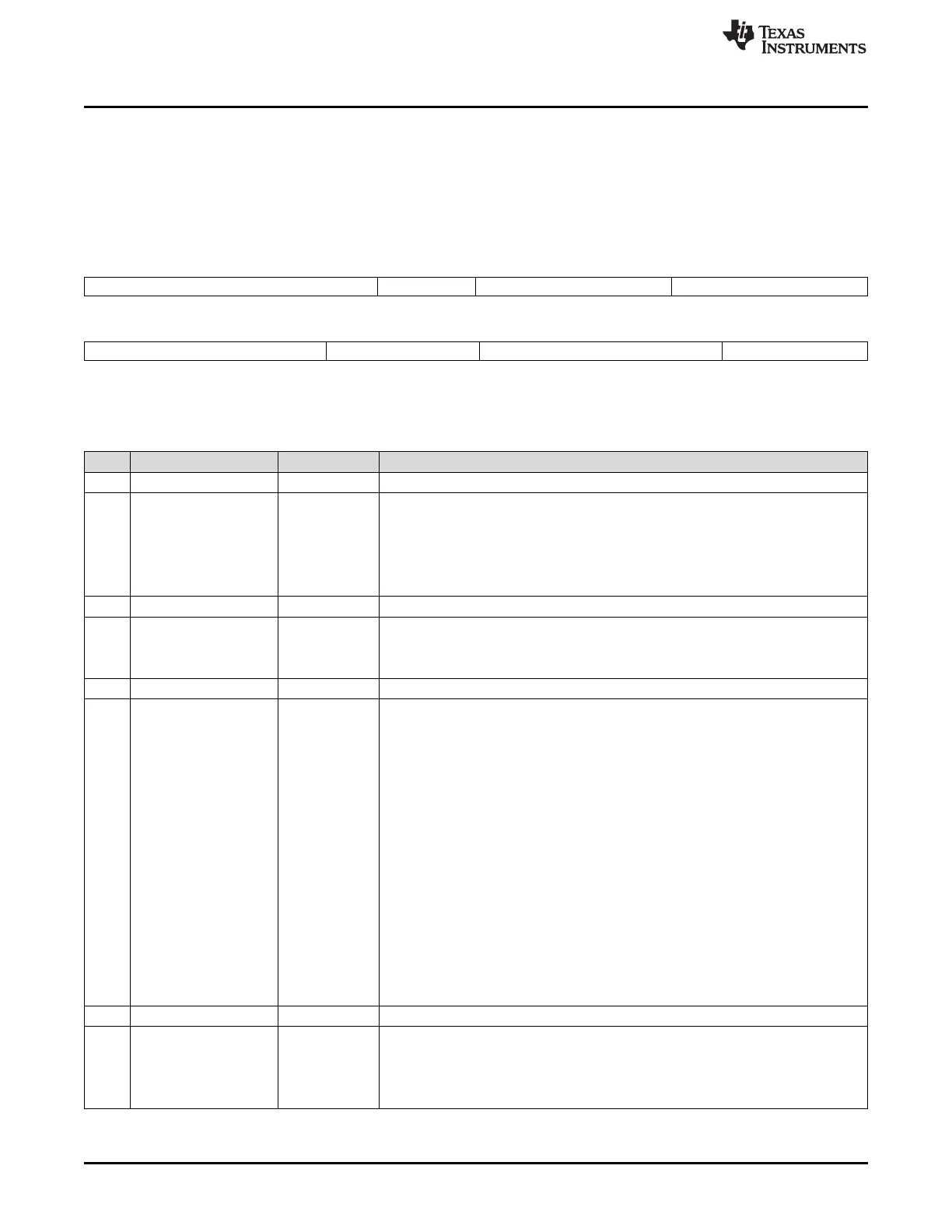

Table 7-35. Diagnostic Control Register (FDIAGCTRL) Field Descriptions

Bit Field Value Description

31-25 Reserved 0 Reads return 0. Writes have no effect.

24 DIAG_TRIG Diagnostic Trigger

Diagnostic trigger is the final qualifier for the diagnostic result. After setting all the

other diagnostic register values, the DIAG_TRIG is set to 1. This activates the

diagnostic logic for one access and then automatically clears the DIAG_TRIG value.

The DIAG_EN_KEY and DIAGMODE bits must be set before setting DIAG_TRIG.

This bit always reads as 0.

23-20 Reserved 0 Reads return 0. Writes have no effect.

19-16 DIAG_EN_KEY Diagnostic Enable Key

5h Diagnostic mode is enabled.

All other values Diagnostic mode is disabled.

15-11 Reserved 0 Reads return 0. Writes have no effect.

10-8 DIAG_BUF_ SEL Diagnostic Buffer Select

0 During diagnostic mode 5 the DIAG_BUF_SEL selects the buffer to read or write when

accessing the FPRIM_ADD_TAG and FDUP_ADD_TAG registers. The address tags

consists of matching primary and duplicate address tag registers. All the primary

address tag registers are memory mapped to a common address (see Section 7.10.8)

and are selected by DIAG_BUF_SEL. The same occurs for the duplicate address (see

Section 7.10.9). Port A has 2 buffers and Port B has 4 buffers.

During diagnostic mode 7 the value selects the port on which to perform the

diagnostic.

0 Port A Buffer 0 (diag mode 5) / Port A selected to flip data/ECC (diag mode 7)

1h Port A Buffer 1 (diag mode 5) / Reserved in diag mode 7

2h Reserved

3h Reserved

4h Port B Buffer 0 (diag mode 5) / Port B selected to flip data/ECC (diag mode 7)

5h Port B Buffer 1 (diag mode 5) / Reserved (diag mode 7)

6h Port B Buffer 2 (diag mode 5) / Reserved (diag mode 7)

7h Port B Buffer 3 (diag mode 5) / Reserved (diag mode 7)

7-4 Reserved 0 Reads return 0. Writes have no effect.

2-0 DIAGMODE Diagnostic Mode (Only values 0, 5, and 7 are valid. Other values are reserved).

0 Diagnostic mode is disabled. This is the same as DIAG_EN_KEY is not equal to 5h.

5h Address Tag Register test mode (see Section 7.7.2.1).

7h ECC Data Correction Diagnostic test mode (see Section 7.7.2.2).

Loading...

Loading...