Flash Control Registers

www.ti.com

358

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

F021 Level 2 Flash Module Controller (L2FMC)

7.10.3 EEPROM Error Correction Control Register (EE_FEDACCTRL1)

When a EEPROM bank is erased or zeroed out, the contents will be all 1's or all 0's, respectively. In such

a case, the ECC will be incorrect. EE_FEDACCTRL1 lets the L2FMC ignore an all 1's and all 0's

condition, on reads from the EEPROM bank.

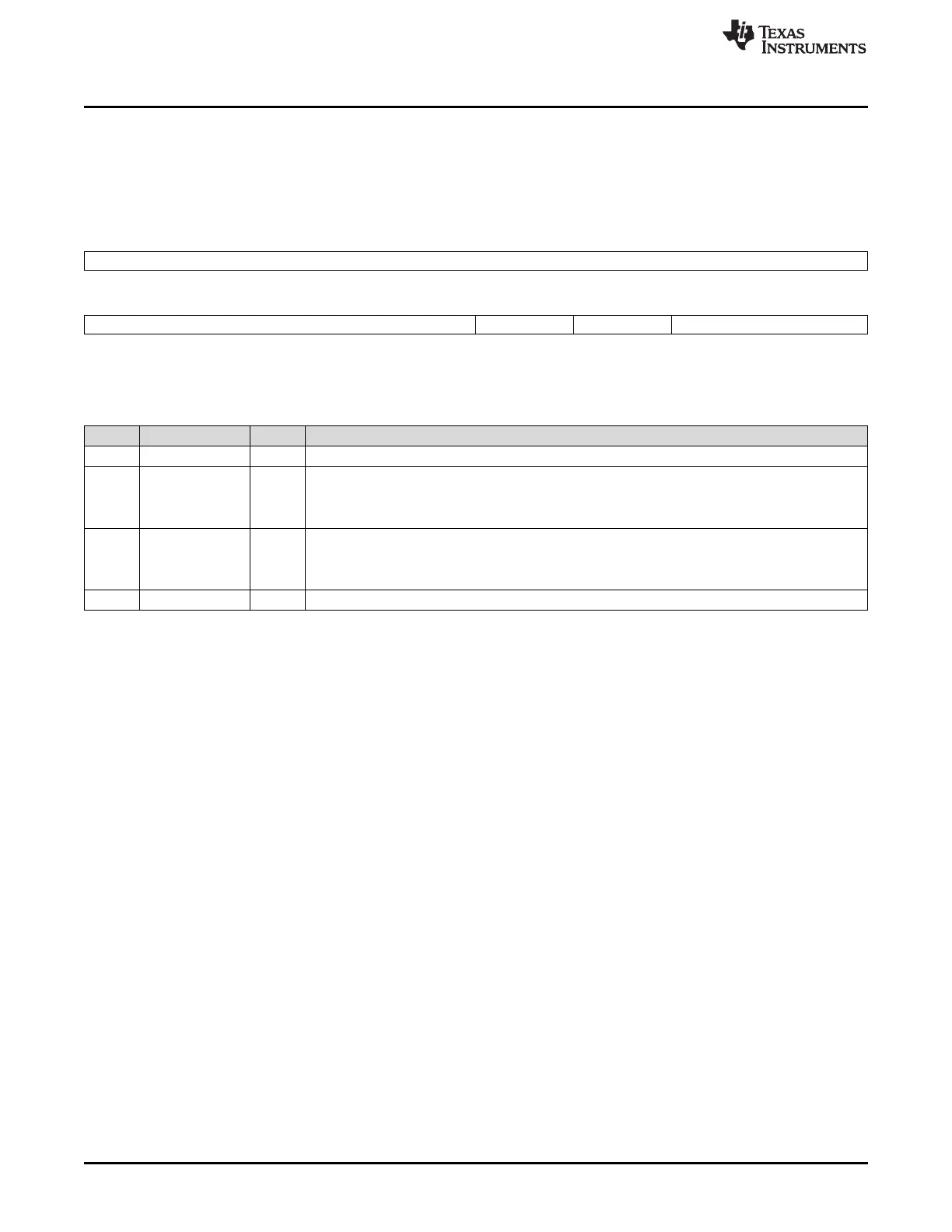

Figure 7-13. EEPROM Error Correction Control Register (EE_FEDACCTRL1) (offset = 08h)

31 16

Reserved

R-0

15 6 5 4 3 0

Reserved EOCV EZCV Reserved

R-0 R/WP-0 R/WP-0 R-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in Privilege Mode; -n = value after reset

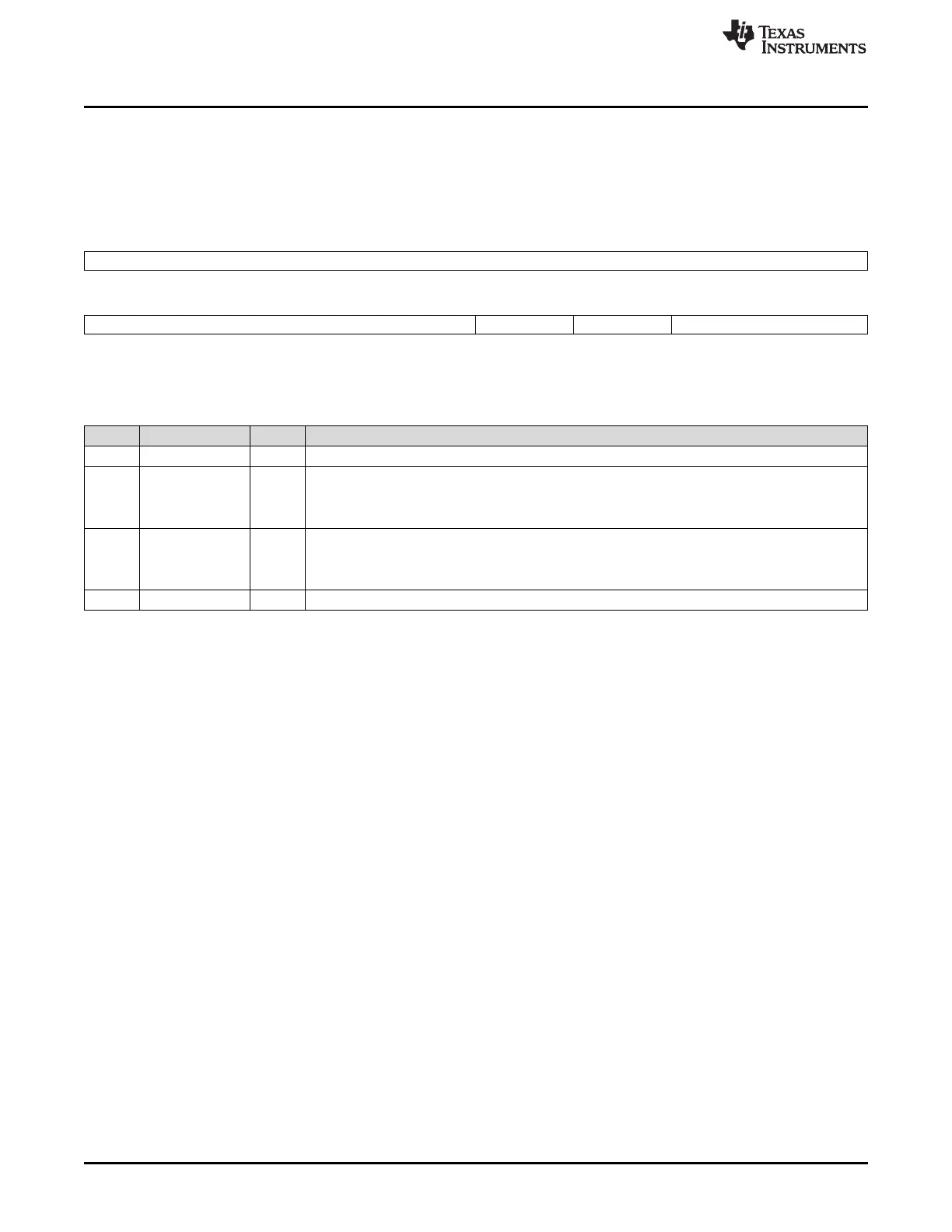

Table 7-15. EEPROM Error Correction Control Register (EE_FEDACCTRL1) Field Descriptions

Bit Field Value Description

31-6 Reserved 0 Reads return 0. Writes have no effect.

5 EOCV One condition valid

0 DO NOT allow the condition of all data bits and ECC bits to be 1.

1 Allow the condition of all data bits and ECC bits to be 1.

4 EZCV Zero condition valid

0 DO NOT allow the condition of all data bits and ECC bits to be 0.

1 Allow the condition of all data bits and ECC bits to be 0.

3-0 Reserved 0 Reads return 0. Writes have no effect.

Loading...

Loading...