HTU Control Registers

www.ti.com

1150

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer Transfer Unit (HTU) Module

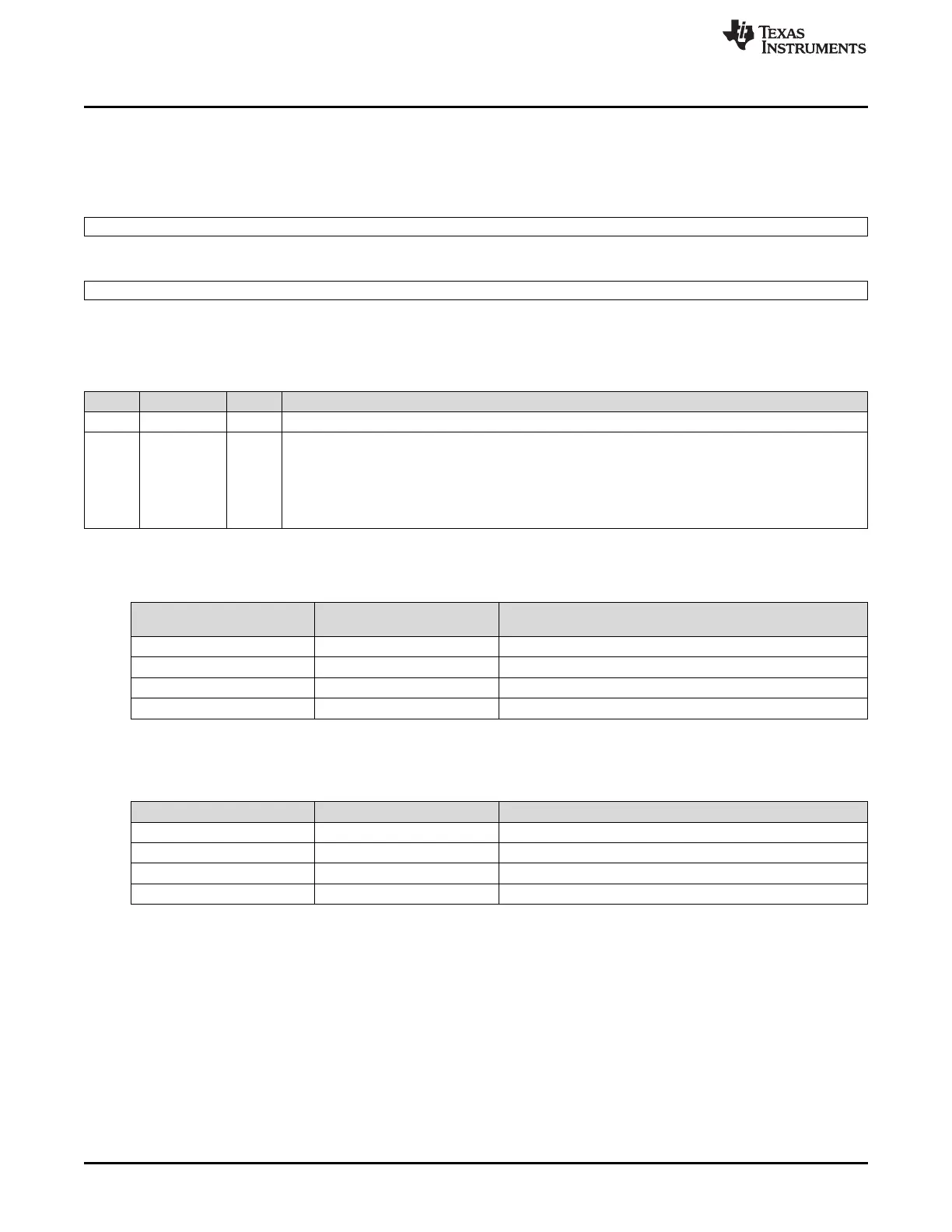

24.4.2 Control Packet Enable Register (HTU CPENA)

This register enables or disables the individual double control packets (DCP).

Figure 24-15. Control Packet Enable Register (HTU CPENA) [offset = 04h]

31 16

Reserved

R-0

15 0

CPENA

R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privilege mode only; -n = value after reset

Table 24-12. Control Packet Enable Register (HTU CPENA) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reads return 0. Writes have no effect.

15-0 CPENA CP Enable Bits

Bits (2*x) and (2*x+1) of CPENA control the double control packet (DCP) x (whereby x must be within

0,1,....,7).

See Table 24-13 for write rules.

See Table 24-14 for read rules.

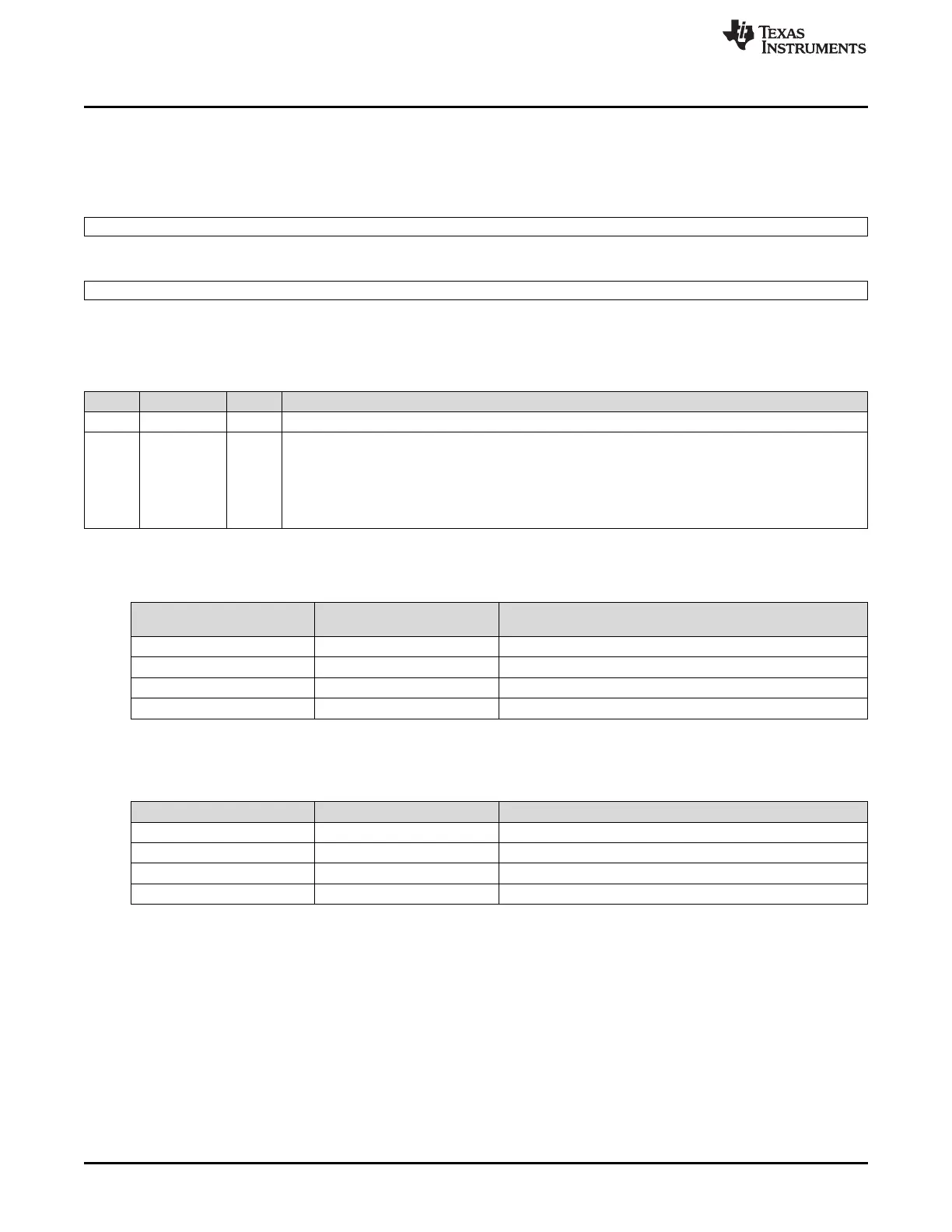

Table 24-13. CPENA Write Results

Bit (2*x+1) Bit (2*x)

Control packets (CP) B and A of DCP x are affected as

follows:

0 0 CP B and A are not changed.

0 1 CP B is disabled and CP A are enabled simultaneously.

1 0 CP B is enabled and CP A are disabled simultaneously.

1 1 CP B and CP A are both disabled simultaneously.

Table 24-14. CPENA Read Results

Bit (2*x+1) Bit (2*x) State of DCP:

0 0 The DCP is disabled.

0 1 CP B is disabled and CP A is enabled.

1 0 CP B is enabled and CP A is disabled.

1 1 Cannot be read.

• The conditions listed in Section 24.2.3 can automatically disable DCP x. In this case, bits (2*x) and

(2*x+1) are both automatically set to 0.

• When bits (2*x) and (2*x+1) change from 00 to 01 or from 00 to 10 caused by a write access to

CPENA, then old pending requests on the corresponding request line are cleared. This means only

new requests which occur after this write access cause the first HTU transfer for this DCP. This is not

the case when switching CPs (from 10 to 01 or from 01 to 10).

• CP A and/or CP B of a DCP can be configured to one-shot, circular or auto-switch transfer mode via

the TMBA or TMBB bits in the IHADDRCT control packet configuration. If a write access to CPENA

occurs during the last frame of a buffer (with frame counter = 1) then the action defined by the write

access to CPENA and the action defined by TMBx can contradict. The priority rules for this case are

given in Table 24-1.

Loading...

Loading...