Summary of L2FMC Errors

www.ti.com

354

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

F021 Level 2 Flash Module Controller (L2FMC)

7.9 Summary of L2FMC Errors

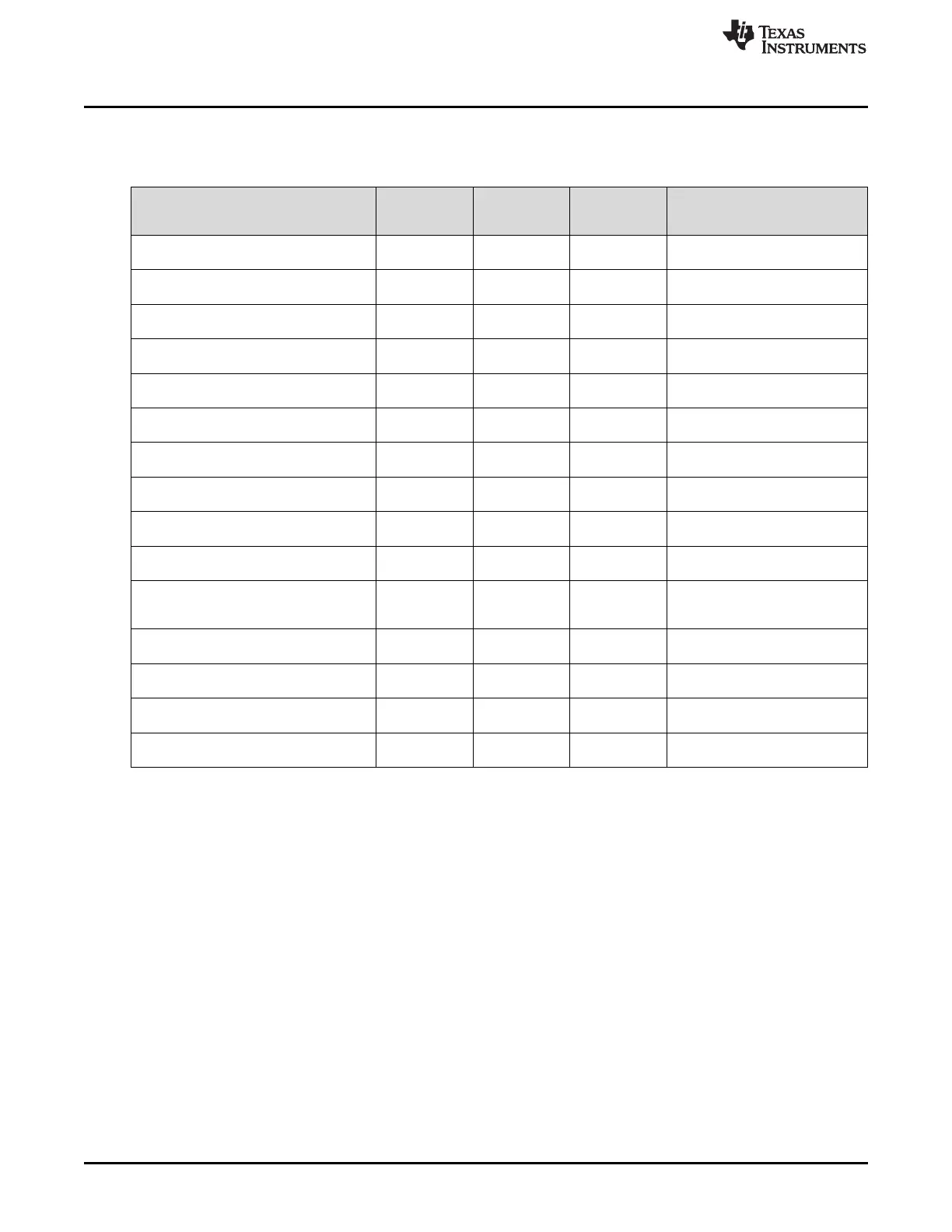

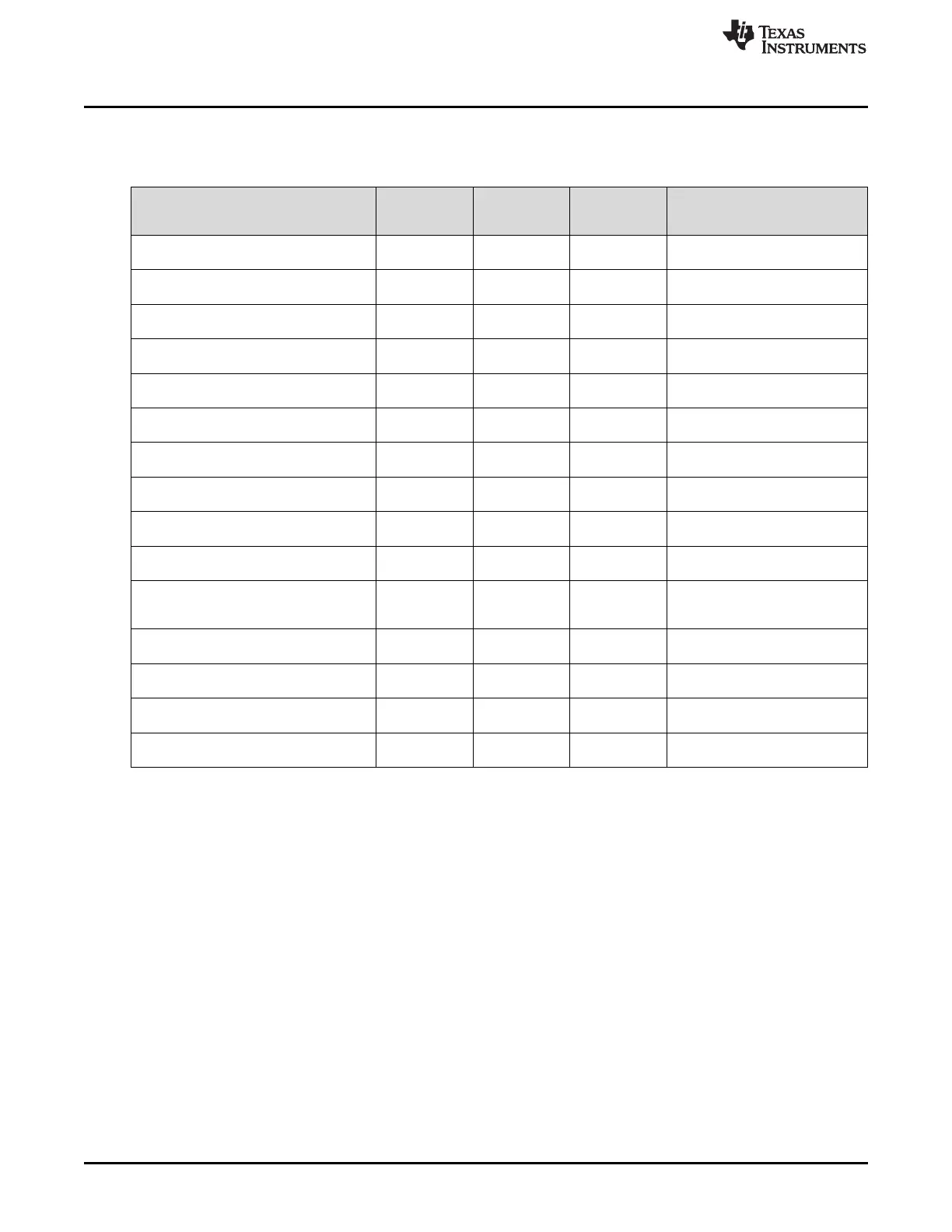

Table 7-11. Errors in L2FMC

Scenario

Does this

error cause a

Bus Error?

Does this

error go to

ESM?

Is a flag in

L2FMC set?

Name of Flag

Access parity error/Internal parity errors Yes Yes Yes

FEDAC_PxSTATUS.

ADD_PAR_ERR

Port A/B Idle State parity error No Yes Yes

FEDAC_PxSTATUS.

MCMD_PAR_ERR

Address tag error Yes Yes Yes

FEDAC_PxSTATUS.

ADD_TAG_ERR

Access to Flash space beyond available

size

Yes No No -

Access to Flash while pump/bank are not

active

Yes No No -

Flash Access time-out Yes Yes Yes

FEDAC_PxSTATUS.

ACC_TOUT

Invalid access to L2FMC (for example,

writes)

Yes No No -

Single-bit Error during Implicit Reads No Yes Yes

FEDAC_GBLSTATUS.

IMPLICIT_COR_ERR

Uncorrectable Error during Implicit Reads No Yes Yes

FEDAC_GBLSTATUS.

IMPLICIT_UNC_ERR

Access to bank while program/erase

operations are ongoing on the same bank

Yes No No -

Access to register address offsets

between 2C8h and 3FFh or 4B8h and

7FFh

Yes No No -

Redirected access to POM received a bus

error

Yes No No -

Response of redirected access to POM

has access parity error

Yes No Yes POMFLG.PERR_Px

POM Idle State parity error No Yes Yes

FEDAC_PxSTATUS.

MCMD_PAR_ERR

Soft Errors in high integrity bits carrying

Implicit read data

No Yes Yes

FEDAC_GBLSTATUS.

RCR_ERR

Loading...

Loading...