www.ti.com

ADC Registers

947

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Analog To Digital Converter (ADC) Module

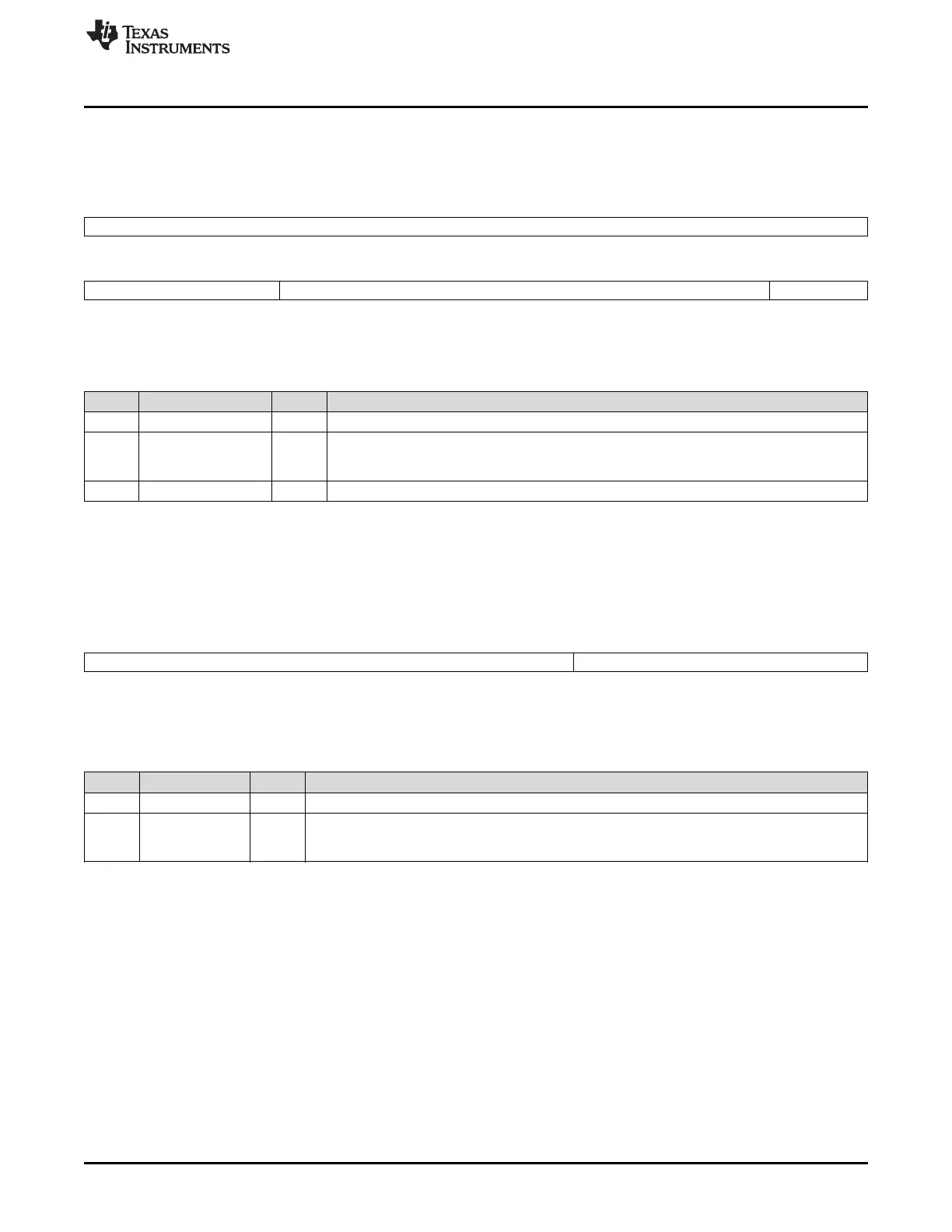

22.3.67 ADC Parity Error Address Register (ADPARADDR)

ADC Parity Error Address Register (ADPARADDR) is shown inFigure 22-98 and described in Table 22-73.

Figure 22-98. ADC Parity Error Address Register (ADPARADDR) [offset = 184h]

31 16

Reserved

R-0

15 12 11 2 1 0

Reserved ERROR_ADDRESS Reserved

R-0 R-U R-0

LEGEND: R = Read only; -n = value after reset; U = value after reset is unknown

Table 22-73. ADC Parity Error Address Register (ADPARADDR) Field Descriptions

Bit Field Value Description

31-12 Reserved 0 Reads return 0. Writes have no effect.

11-2 ERROR_ADDRESS These bits hold the address of the first parity error generated in the ADC results ' RAM. This

error address is frozen from being updated until it is read by the application. In emulation mode,

this address is maintained frozen even when read.

1-0 Reserved 0 Reads return 0. Writes have no effect. Reading [11:0] provides the 32-bit aligned address.

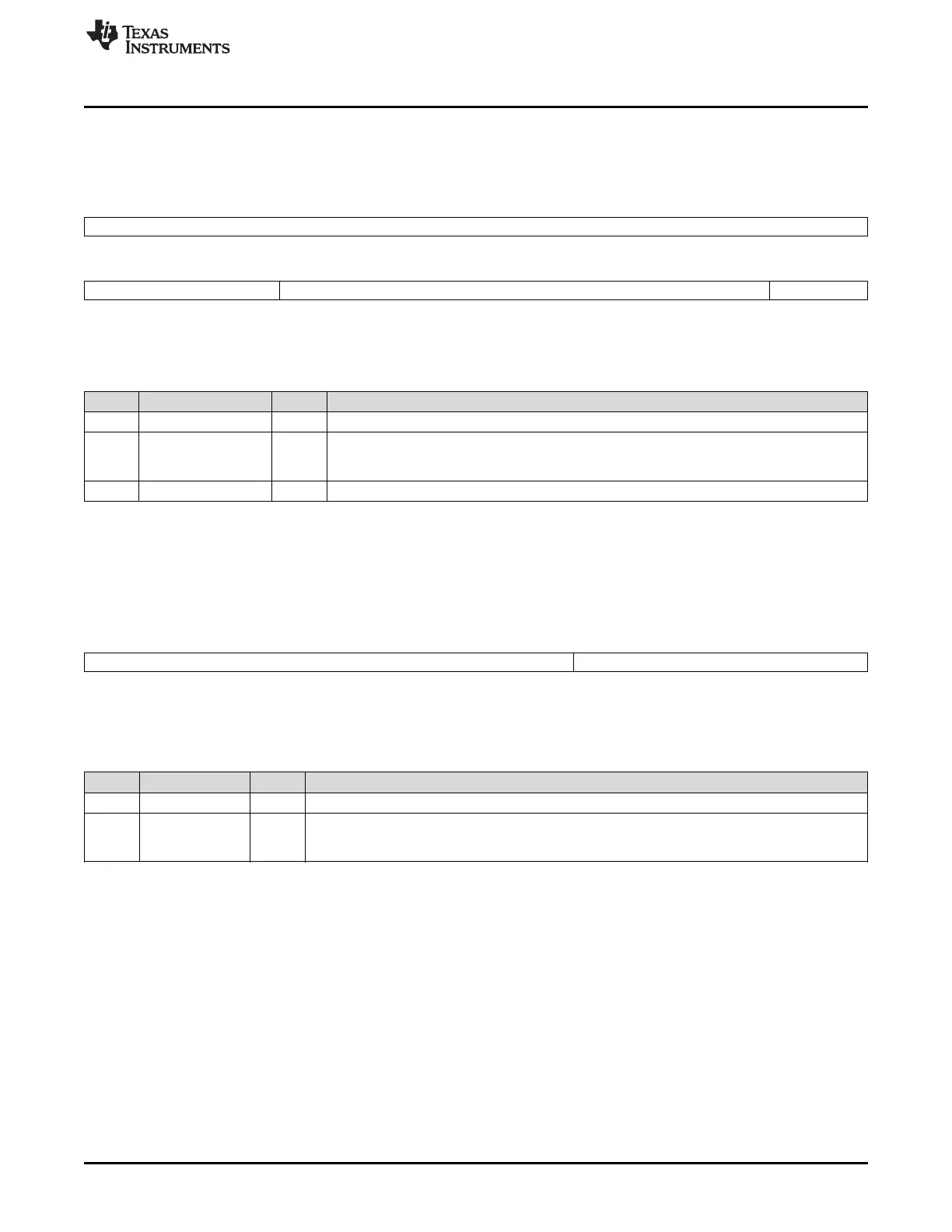

22.3.68 ADC Power-Up Delay Control Register (ADPWRUPDLYCTRL)

Figure 22-99 and Table 22-74 describe the ADPWRDLYCTRL register.

Figure 22-99. ADC Power-Up Delay Control Register (ADPWRUPDLYCTRL) [offset = 188h]

31 10 9 0

Reserved PWRUP_DLY

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 22-74. ADC Power-Up Delay Control Register (ADPWRUPDLYCTRL) Field Descriptions

Bit Field Value Description

31-10 Reserved 0 Reads return 0. Writes have no effect.

9-0 PWRUP_DLY This register defines the number of VCLK cycles that the ADC state machine has to wait after

releasing the ADC core from power down before starting a new conversion. Refer to

Section 22.2.6.3 for more details.

Loading...

Loading...