NMPU Registers

www.ti.com

474

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

System Memory Protection Unit (NMPU)

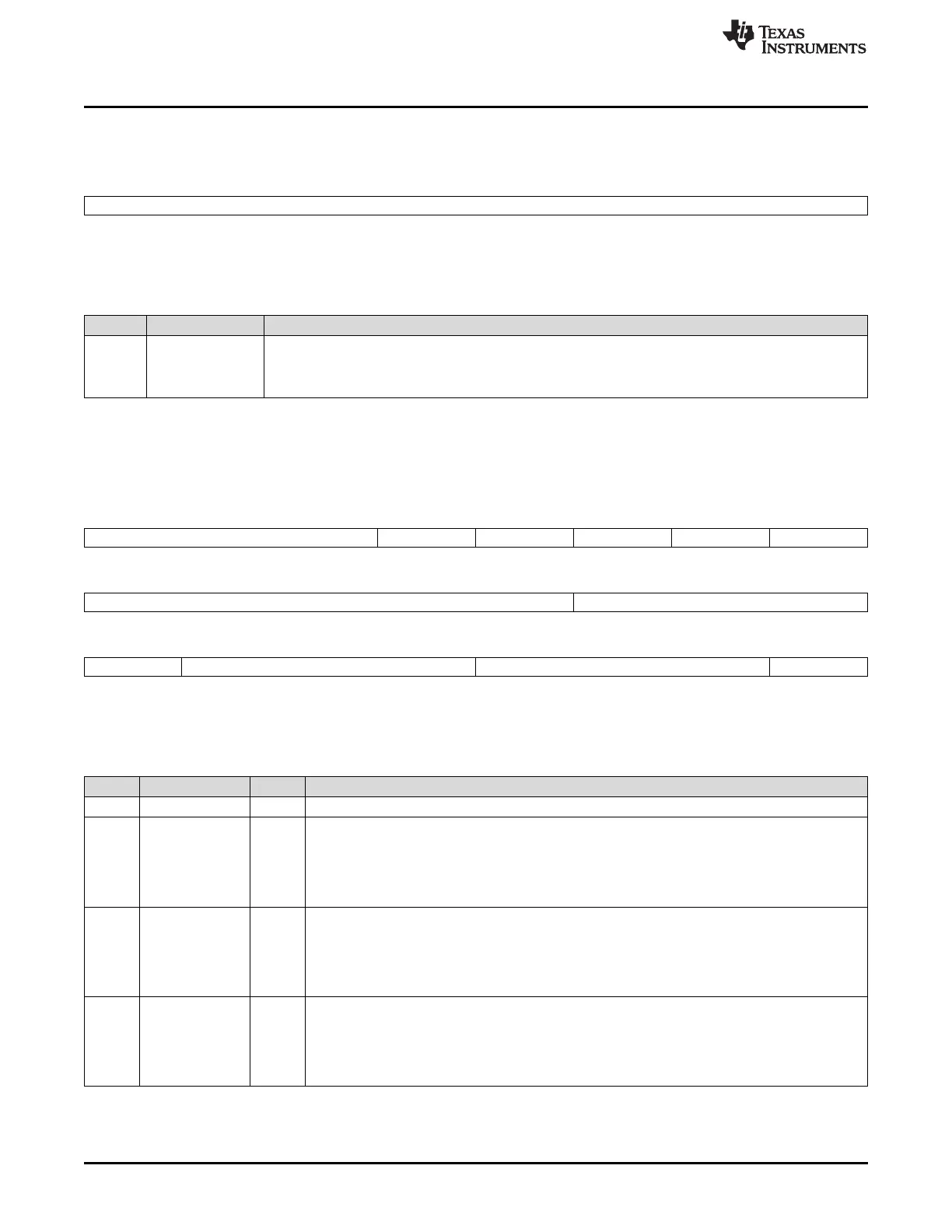

11.4.4 MPU Diagnostic Address Register (MPUDIAGADDR)

Figure 11-7. MPU Diagnostic Address Register (MPUDIAGADDR) [offset = 0Ch]

31 0

DIAG ADDRESS

R/WP-0

LEGEND: R/W = Read/Write; WP = Write in privileged mode only; -n = value after reset

Table 11-7. MPU Diagnostic Address Register (MPUDIAGADDR) Field Descriptions

Bit Field Description

31-0 DIAG ADDRESS Diagnostic address. This register is used in diagnostic mode.

Read: Returns the current value of diagnostic address.

Write in Privilege: Address to be used for diagnostic mode to check the address comparator logic.

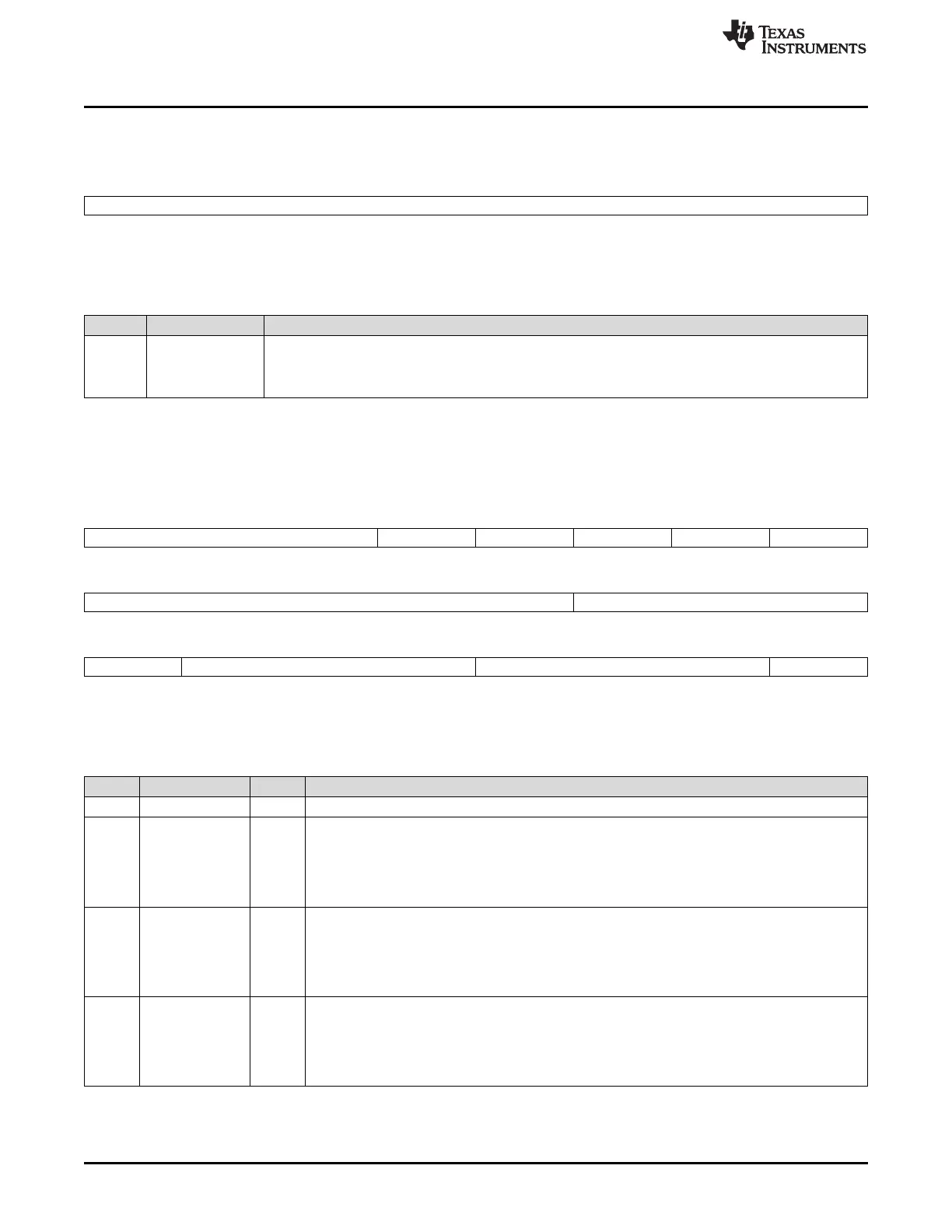

11.4.5 MPU Error Status Register (MPUERRSTAT)

Figure 11-8. MPU Error Status Register (MPUERRSTAT) [offset = 10h]

31 29 28 27 26 25 24

Reserved RERR WERR BGERR APERR Reserved

R-0 R-0 R-0 R-0 R-0 R-0

23 19 18 16

Reserved REGION

R-0 R-0

15 14 13 8 7 1 0

Reserved MASTERID Reserved ERRFLAG

R-0 R-0 R-0 R/W1CP-0

LEGEND: R/W = Read/Write; R = Read only; W1CP = Write 1 to clear in privilege mode only; -n = value after reset

Table 11-8. MPU Error Status Register (MPUERRSTAT) Field Descriptions

Bit Field Value Description

31-29 Reserved 0 Reserved. Reads return 0.

28 RERR Read Error. This field is valid only when the APERR or BGERR bit is 1. This field is read only and

is automatically reset by clearing the ERRFLAG bit. This field is not updated when the ERRFLAG

bit is set. Writes have no effect.

0 MPU compare fail did not occur on a read access.

1 MPU compare fail occurred on a read access.

27 WERR Write Error. This field is valid only when the APERR or BGERR bit is 1. This field is read only and is

automatically reset by clearing the ERRFLAG bit. This field is not updated when the ERRFLAG bit

is set. Writes have no effect.

0 MPU compare fail did not occur on a write access.

1 MPU compare fail occurred on a write access.

26 BGERR Background Error. This field is read only and is automatically reset by clearing the ERRFLAG bit.

This field is not updated when the ERRFLAG bit is set. Writes have no effect.

0 There was no memory access to addresses that are outside all the enabled MPU regions.

1 MPU compare fail generated because of access to an address that is outside all the enabled MPU

regions.

Loading...

Loading...