NMPU Registers

www.ti.com

476

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

System Memory Protection Unit (NMPU)

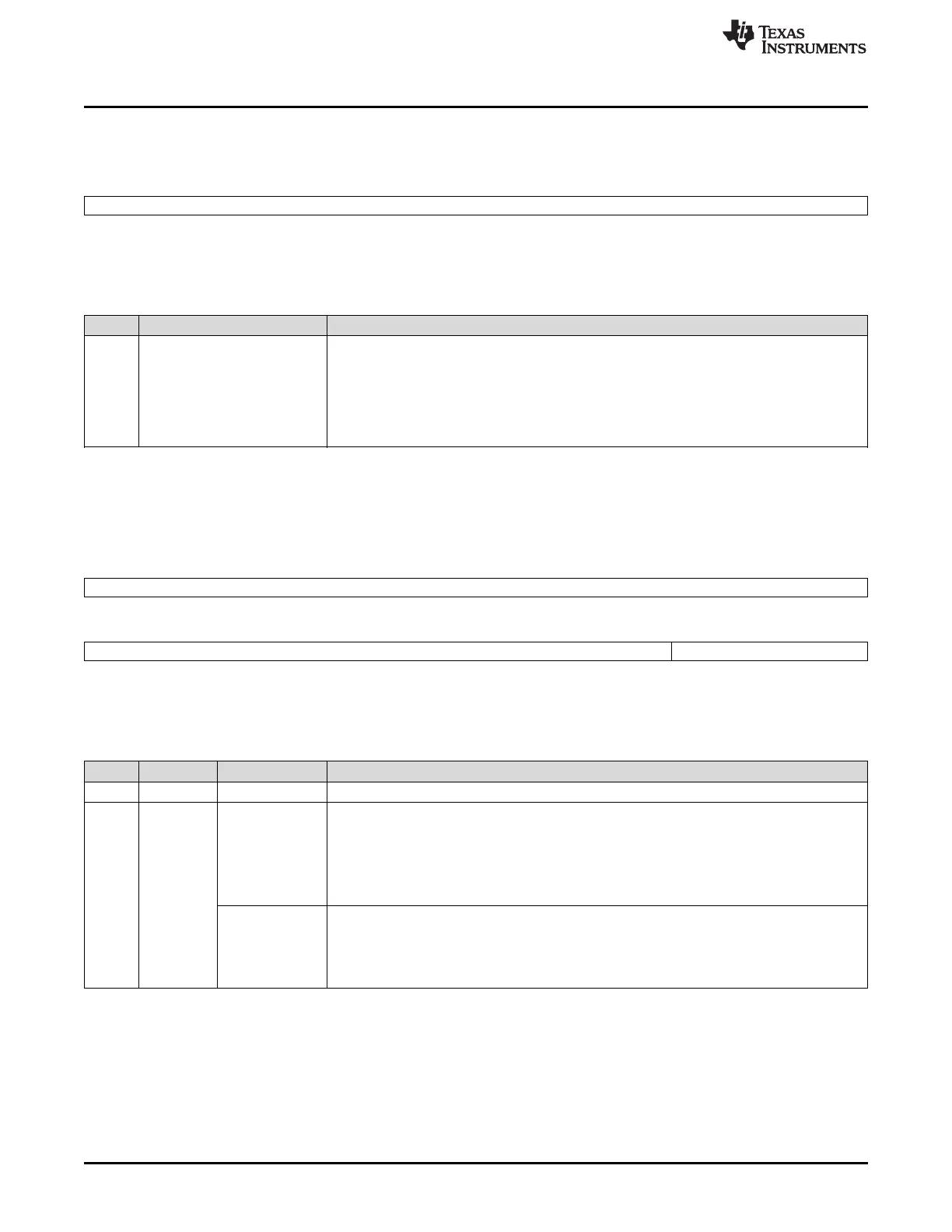

11.4.6 MPU Error Address Register (MPUERRADDR)

Figure 11-9. MPU Error Address Register (MPUERRADDR) [offset = 14h]

31 0

COMPARE FAIL ADDRESS

R-0

LEGEND: R = Read only; -n = value after reset

Table 11-9. MPU Error Address Register (MPUERRADDR) Field Descriptions

Bit Field Description

31-0 COMPARE FAIL ADDRESS Address for MPU compare fail. This field is valid only when the ERRFLAG bit in the MPU error

status register (MPUERRSTAT) is set and the APERR or BGERR bit in MPUERRSTAT register

is 1. This field is read only and is automatically reset by clearing the ERRFLAG bit in

MPUERRSTAT register. This field is not updated when the ERRFLAG bit is set. Once the

ERRFLAG bit is cleared, this field gets updated for the next MPU compare fail after clearing the

flag. Writes have no effect.

Shows the address for the first transaction that resulted in a compare fail.

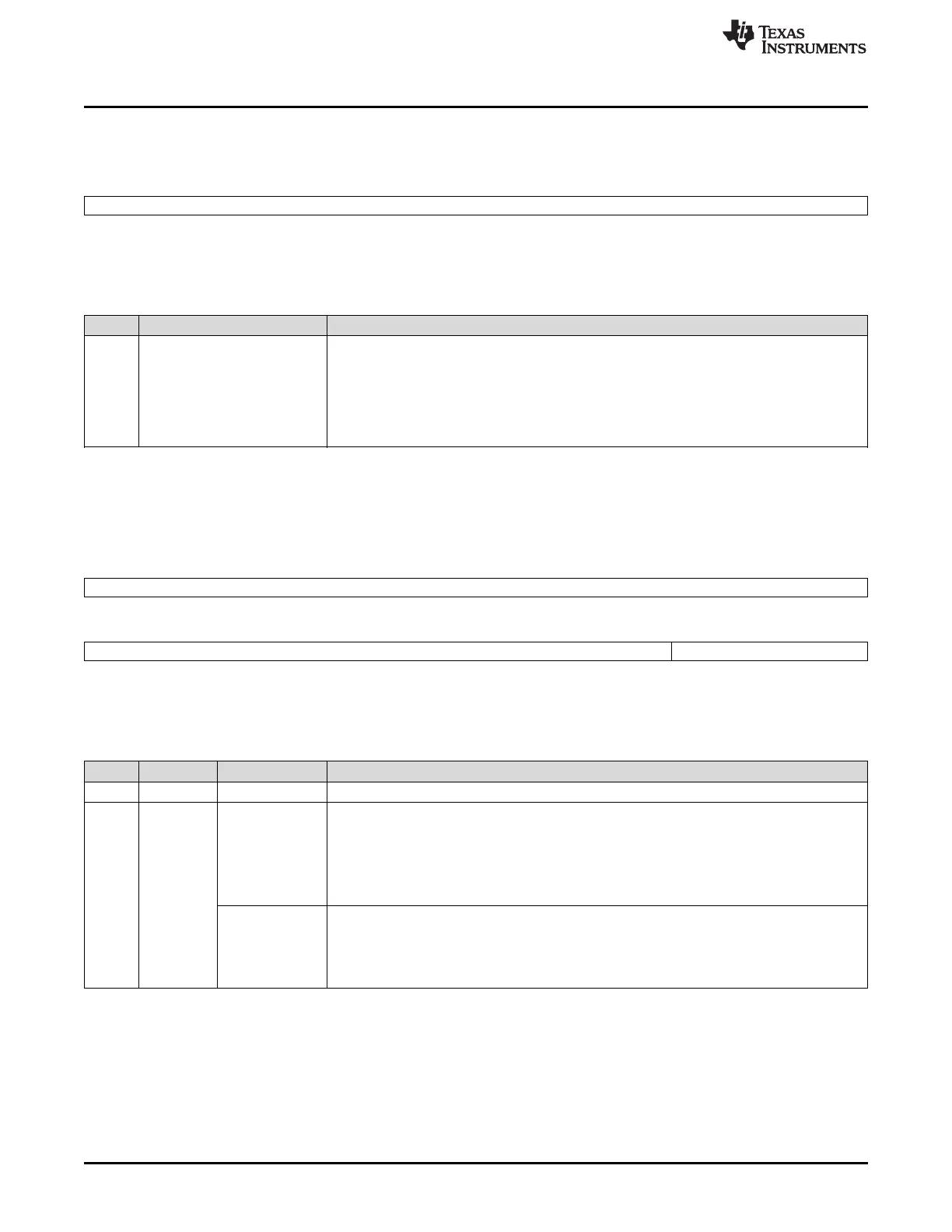

11.4.7 MPU Control Register 1 (MPUCTRL1)

Figure 11-10. MPU Control Register 1 (MPUCTRL1) [offset = 20h]

31 16

Reserved

R-0

15 4 3 0

Reserved MPUENA

R-0 R/WP-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

Table 11-10. MPU Control Register 1 (MPUCTRL1) Field Descriptions

Bit Field Value Description

31-4 Reserved 0 Reserved. Reads return 0.

3-0 MPUENA MPU Enable Key. This is the key for enabling memory protection. This field is updated only if

the write data is 5h or Ah. Register writes are ignored for all other values of write data. All other

configuration registers must be programmed before enabling the MPU.

A built-in correction logic detects single bit soft error on this field and corrects the value in the

next cycle. Functionality and register read data remain the same during the correction cycle.

Read: Returns current value of MPUENA.

Write in Privilege:

5h Memory protection is disabled.

Ah Memory protection is enabled.

All other values Reserved. The bits remain unchanged.

Loading...

Loading...