Control and Status Registers

www.ti.com

402

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Level 2 RAM (L2RAMW) Module

8.3.8 L2RAMW Memory Initialization Domain Register (MEMINIT_DOMAIN)

The MEMINIT_DOMAIN register, shown in Figure 8-9 and described in Table 8-10, stores the address for

which an address-parity error was detected.

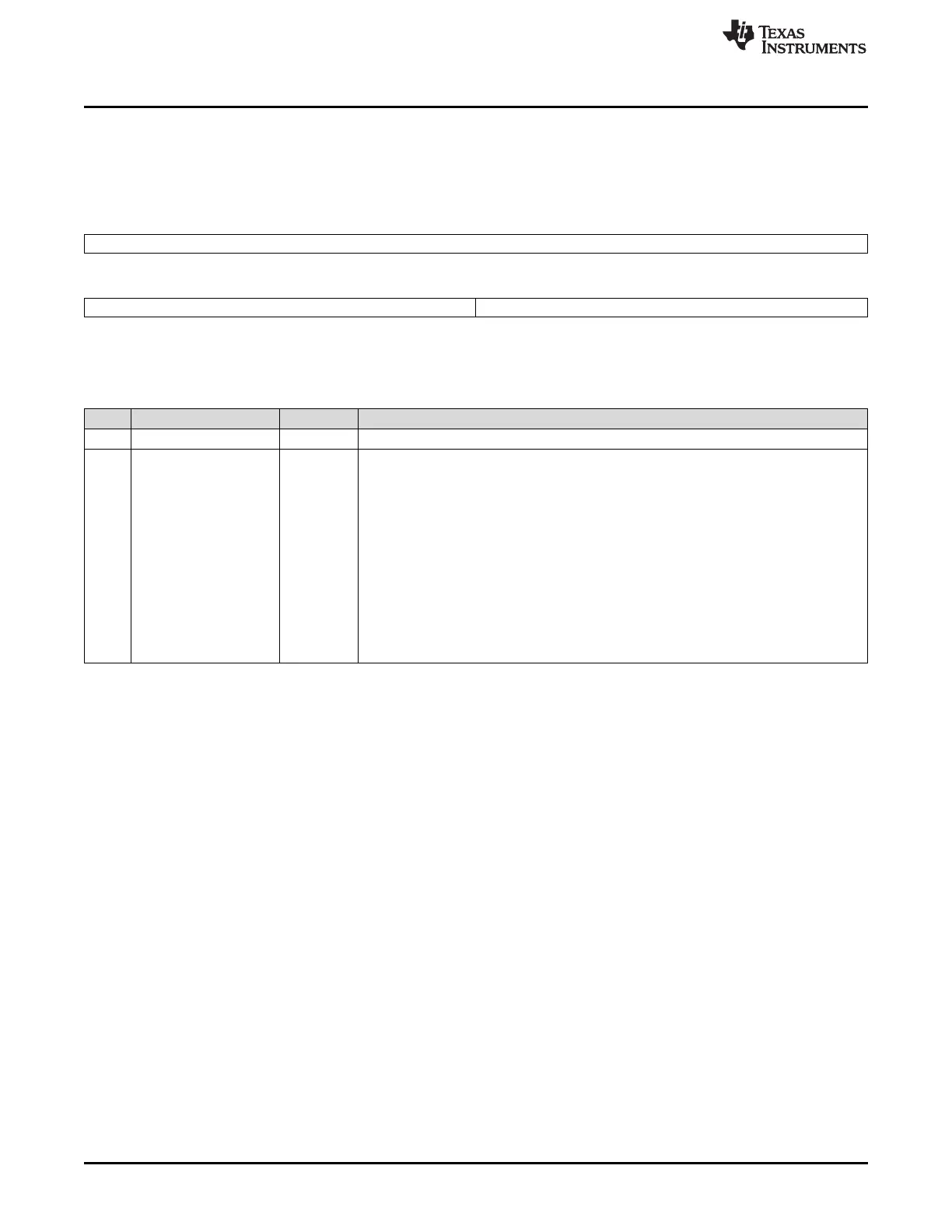

Figure 8-9. L2RAMW Memory Initialization Domain Register (MEMINIT_DOMAIN) (offset = 3Ch)

31 16

Reserved

R-0

15 8 7 0

Reserved MEMINIT_ENA

R-0 R/WP-FFh

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

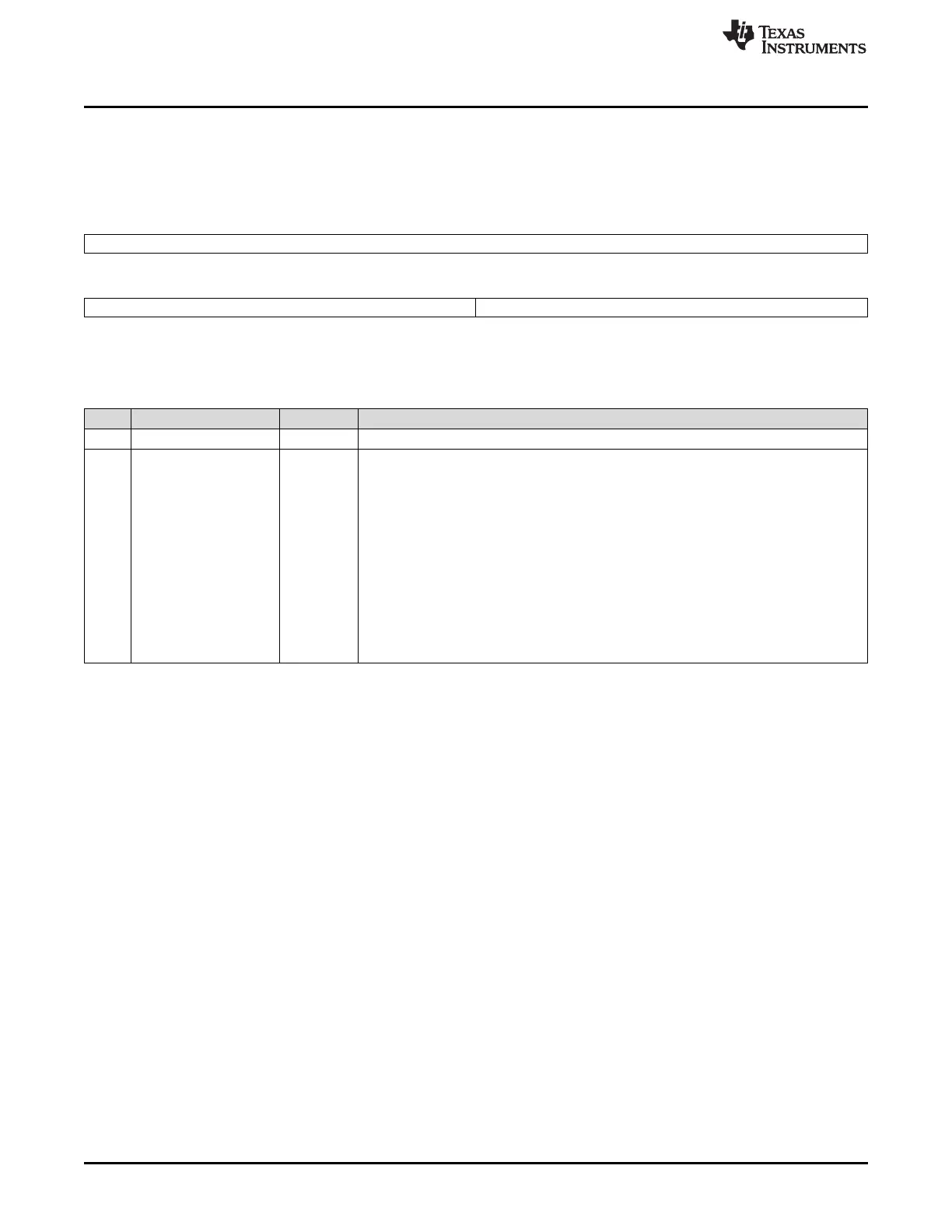

Table 8-10. L2RAMW Memory Initialization Domain Register (MEMINIT_DOMAIN) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reads return 0. Writes have no effect.

7-0 MEMINIT_ENA[n] Memory Initialization Enable. Each bit n corresponds to an individual memory domain. If

the corresponding bit is set to 1 when an initialization of the RAM memory is executed,

then that section of the RAM memory will be initialized. If the corresponding bit is cleared

to 0 when an initialization of the RAM memory is executed, then that section of the RAM

memory will not be affected. After reset, all memory power domains are enabled (set to 1)

by default.

Bit 0: enable bit for power domain 0.

Bit 1: enable bit for power domain 1.

:

Bit 7: enable bit for power domain 7.

1 Enable the memory in this power domain to be initialized.

0 Disable the memory in this power domain from being initialized.

Loading...

Loading...