EMIF Registers

www.ti.com

838

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

External Memory Interface (EMIF)

21.3.11 EMIF Interrupt Mask Clear Register (INTMSKCLR)

The EMIF interrupt mask clear register (INTMSKCLR) is used to disable the Asynchronous Timeout

Interrupt. If read as 1, the AT_MASKED bit in the EMIF interrupt masked register (INTMSK) will be set and

an interrupt will be generated when an Asynchronous Timeout occurs. If read as 0, the AT_MASKED bit

will always read 0 and no interrupt will be generated when an Asynchronous Timeout occurs. Writing a 1

to the AT_MASK_CLR bit disables the Asynchronous Timeout Interrupt. The EMIF on some devices does

not have the EMIF_nWAIT pin, therefore, these registers and fields are reserved on those devices. The

INTMSKCLR is shown in Figure 21-25 and described in Table 21-35.

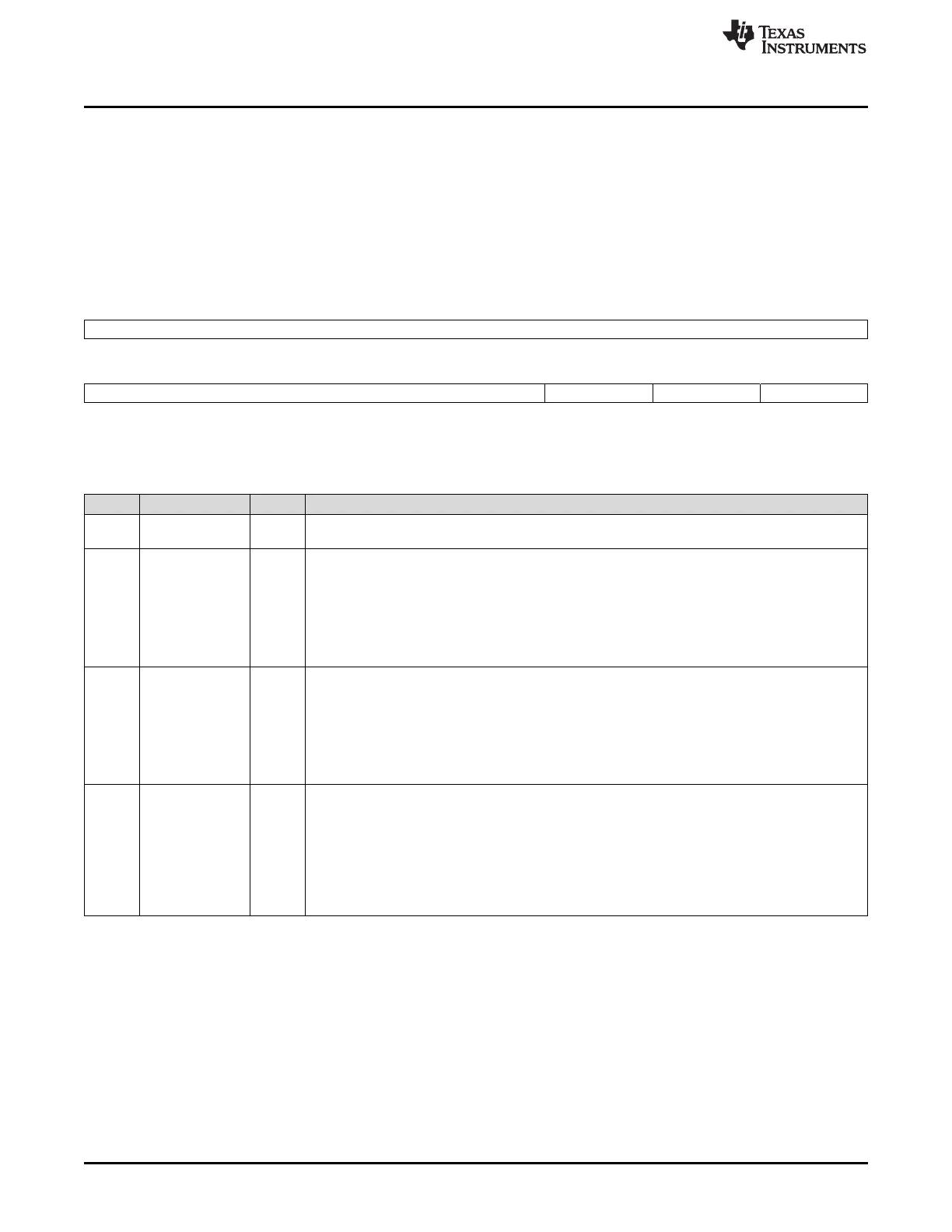

Figure 21-25. EMIF Interrupt Mask Clear Register (INTMSKCLR) [offset = 4Ch]

31 16

Reserved

R-0

15 3 2 1 0

Reserved WR_MASK_CLR LT_MASK_CLR AT_MASK_CLR

R-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

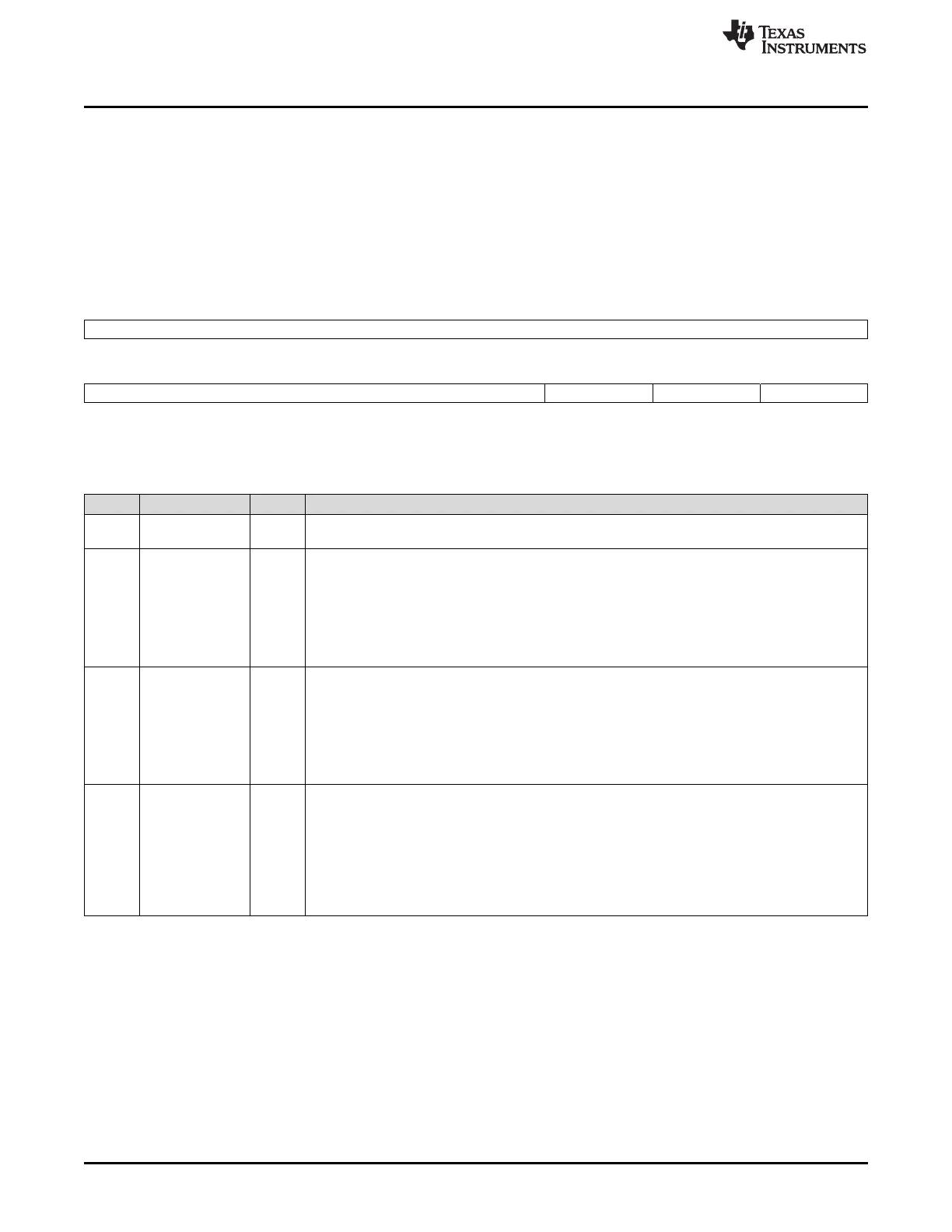

Table 21-35. EMIF Interrupt Mask Clear Register (INTMSKCLR) Field Descriptions

Bit Field Value Description

31-3 Reserved 0 Reserved. The reserved bit location is always read as 0. If writing to this field, always write the

default value of 0.

2 WR_MASK_CLR Wait Rise Mask Clear. This bit determines whether or not the wait rise interrupt is enabled. Writing

a 1 to this bit clears this bit, clears the WR_MASK_SET bit in the EMIF interrupt mask set register

(INTMSKSET), and disables the wait rise interrupt. To set this bit, a 1 must be written to the

WR_MASK_SET bit in INTMSKSET.

0 Indicates that the wait rise interrupt is disabled. Writing a 0 has no effect.

1 Indicates that the wait rise interrupt is enabled. Writing a 1 clears this bit and the WR_MASK_SET

bit in the EMIF interrupt mask set register (INTMSKSET).

1 LT_MASK_CLR Line trap Mask Clear. This bit determines whether or not the line trap interrupt is enabled. Writing a

1 to this bit clears this bit, clears the LT_MASK_SET bit in the EMIF interrupt mask set register

(INTMSKSET), and disables the line trap interrupt. To set this bit, a 1 must be written to the

LT_MASK_SET bit in INTMSKSET.

0 Indicates that the line trap interrupt is disabled. Writing a 0 has no effect.

1 Indicates that the line trap interrupt is enabled. Writing a 1 clears this bit and the LT_MASK_SET bit

in the EMIF interrupt mask set register (INTMSKSET).

0 AT_MASK_CLR Asynchronous Timeout Mask Clear. This bit determines whether or not the Asynchronous Timeout

Interrupt is enabled. Writing a 1 to this bit clears this bit, clears the AT_MASK_SET bit in the EMIF

interrupt mask set register (INTMSKSET), and disables the Asynchronous Timeout Interrupt. To set

this bit, a 1 must be written to the AT_MASK_SET bit of the EMIF interrupt mask set register

(INTMSKSET).

0 Indicates that the Asynchronous Timeout Interrupt is disabled. Writing a 0 has no effect.

1 Indicates that the Asynchronous Timeout Interrupt is enabled. Writing a 1 clears this bit and the

AT_MASK_SET bit in the EMIF interrupt mask set register (INTMSKSET).

Loading...

Loading...