www.ti.com

N2HET Control Registers

1025

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

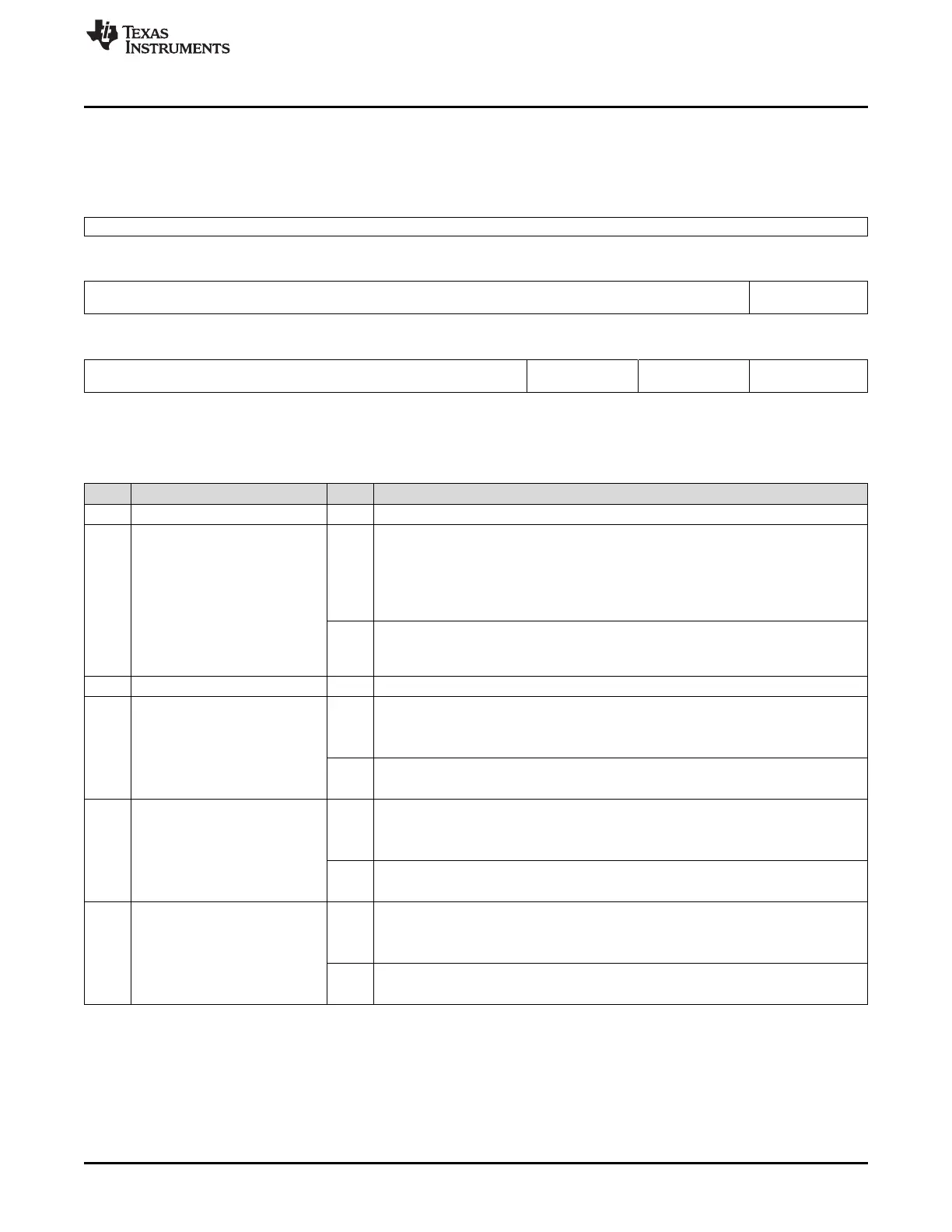

23.4.9 Exception Control Register 2 (HETEXC2)

N2HET1: offset = FFF7 B820h; N2HET2: offset = FFF7 B920h

Figure 23-64. Exception Control Register 2 (HETEXC2)

31 16

Reserved

R-0

15 9 8

Reserved DEBUG_STATUS_

FLAG

R-0 R/WC-0

7 3 2 1 0

Reserved APCNT_OVRFL_

FLAG

APCNT_UNRFL_

FLAG

PRGM_OVRFL_

FLAG

R-0 R/W1C-0 R/W1C-0 R/W1C-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear; -n = value after reset

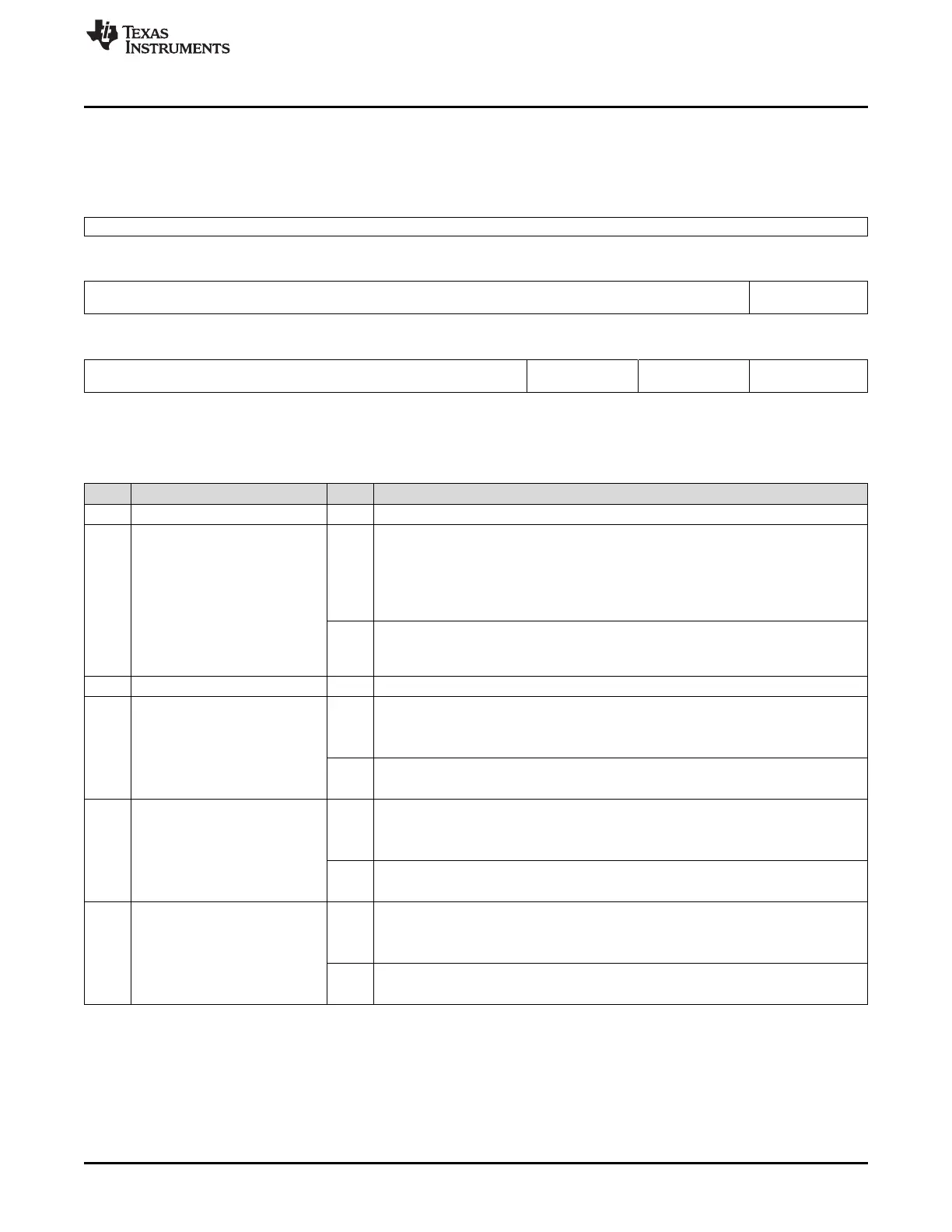

Table 23-25. Exception Control Register 2 (HETEXC2) Field Descriptions

Bit Field Value Description

31-9 Reserved 0 Reads return 0. Writes have no effect.

8 DEBUG_STATUS_FLAG Debug Status Flag.

This flag is set when N2HET has stopped at a breakpoint. Also generates a debug

request to halt the ARM CPU.

0 Read: N2HET is either running, or stopped, flag cleared but not yet restarted.

Write: No effect.

1 Read: N2HET is stopped at a breakpoint.

Write: Clears the bit. To restart N2HET clear this bit and then restart the ARM CPU.

The N2HET and ARM CPU will start synchronously.

7-3 Reserved 0 Reads return 0. Writes have no effect.

2 APCNT_OVRFL_FLAG APCNT Overflow Flag

0 Read: Exception has not occurred since the flag was cleared.

Write: No effect.

1 Read: Exception has occurred since the flag was cleared.

Write: Clears the bit.

1 APCNT_UNDFL_FLAG APCNT Underflow Flag

0 Read: Exception has not occurred since the flag was cleared.

Write: No effect.

1 Read: Exception has occurred since the flag was cleared.

Write: Clears the bit.

0 PRGM_OVERFL_FLAG Program Overflow Flag

0 Read: Exception has not occurred since the flag was cleared.

Write: No effect.

1 Read: Exception has occurred since the flag was cleared

Write: Clears the bit.

Loading...

Loading...