Flash Control Registers

www.ti.com

380

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

F021 Level 2 Flash Module Controller (L2FMC)

7.10.31 FSM Register Write Enable Register (FSM_WR_ENA)

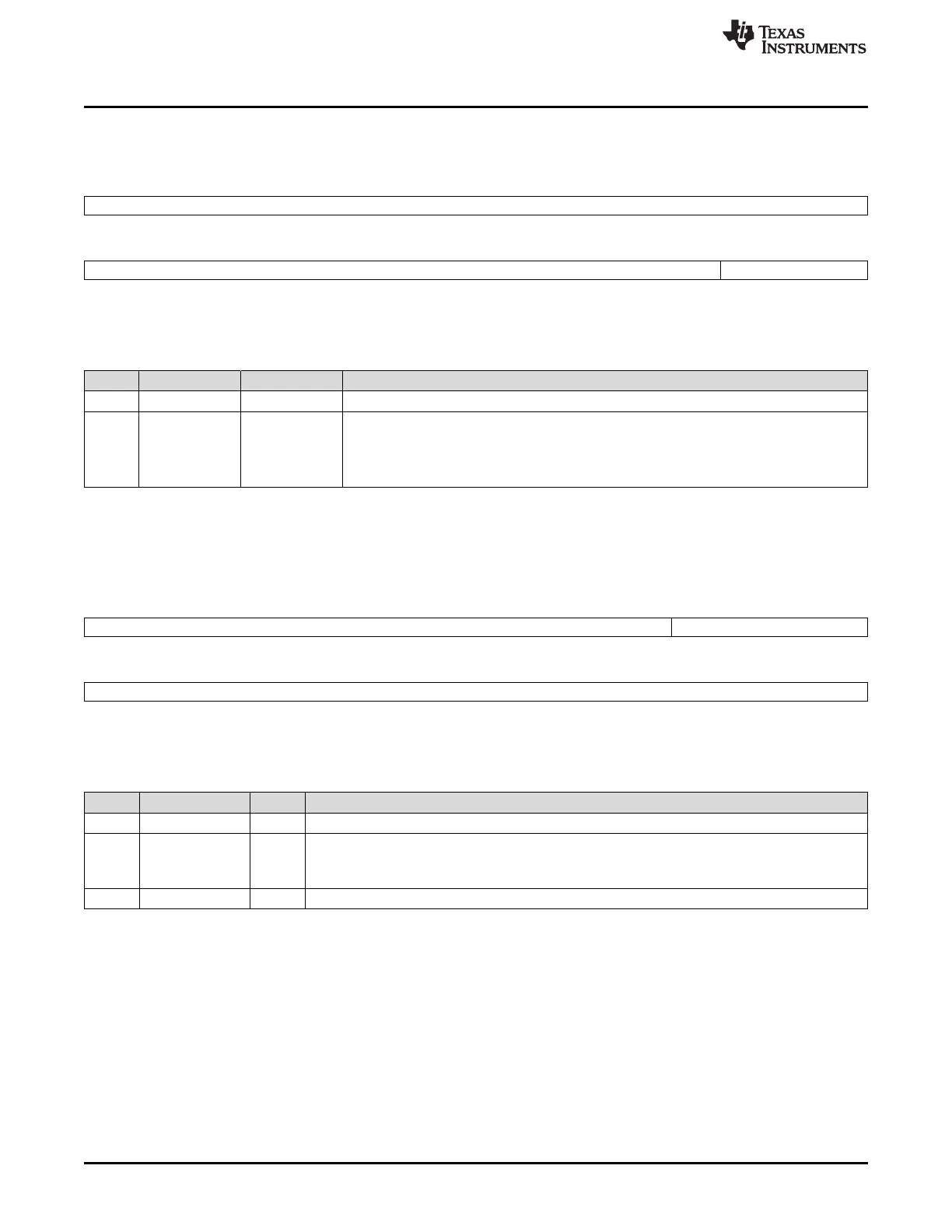

Figure 7-41. FSM Register Write Enable Register (FSM_WR_ENA) (offset = 288h)

31 16

Reserved

R-0

15 3 2 0

Reserved WR_ENA

R-0 R/WP-2h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in Privilege Mode; -n = value after reset

Table 7-43. FSM Register Write Enable Register (FSM_WR_ENA) Field Descriptions

Bit Field Value Description

31-3 Reserved 0 Reads return 0. Writes have no effect.

2-0 WR_ENA FSM Write Enable

5h This register must contain 5h in order to write to any other register in the range FFF8 7200h

to FFF8 72FFh. This is the first register to be written when setting up the FSM.

All other values For all other values, the FSM registers cannot be written.

7.10.32 EEPROM Emulation Configuration Register (EEPROM_CONFIG)

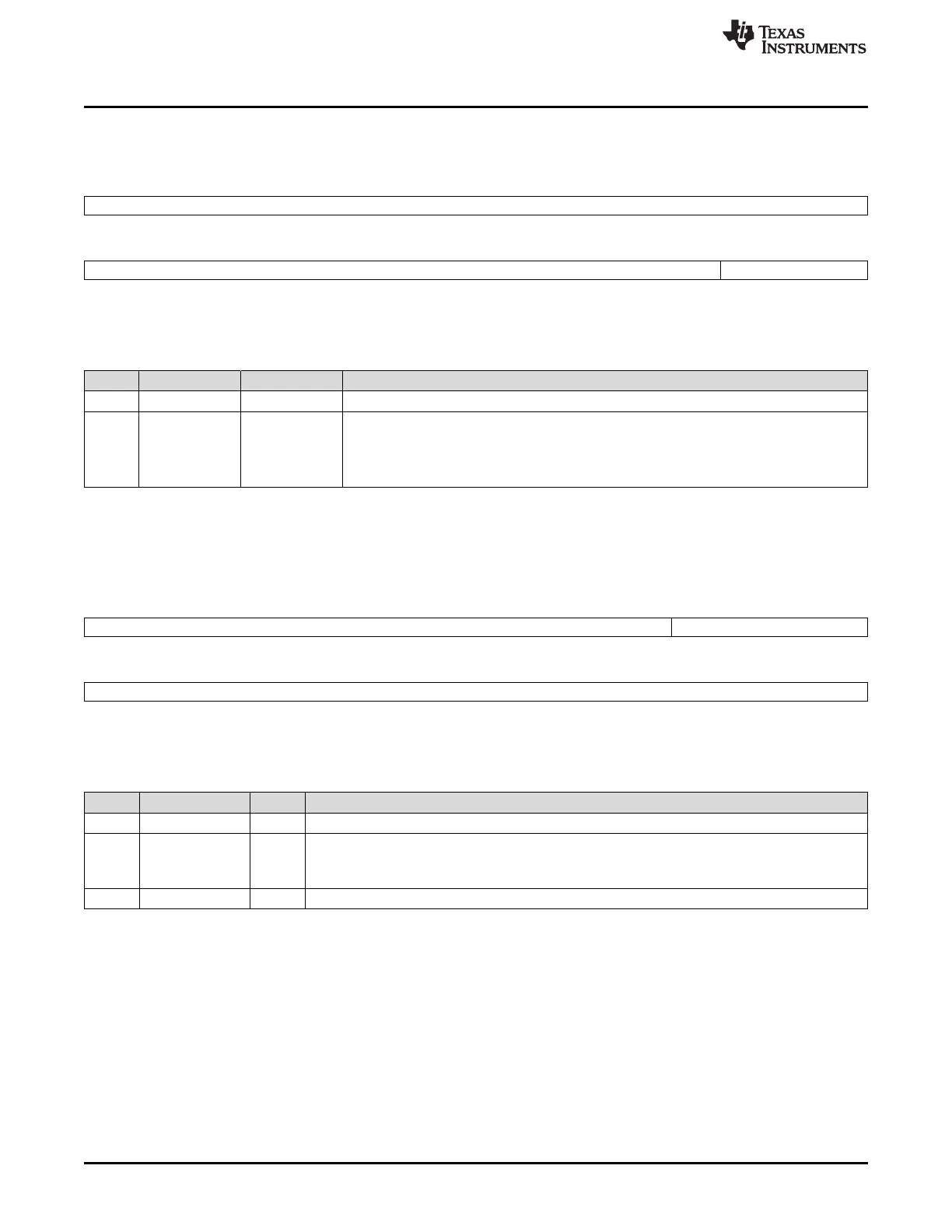

Figure 7-42. EEPROM Emulation Configuration Register (EEPROM_CONFIG) (offset = 2B8h)

31 20 19 16

Reserved EWAIT

R-0 R/WP-1

15 0

Reserved

R-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in Privilege Mode; -n = value after reset

Table 7-44. EPROM Emulation Configuration Register (EEPROM_CONFIG) Field Descriptions

Bit Field Value Description

31-20 Reserved 0 Reads return 0. Writes have no effect.

19-16 EWAIT 0-Fh EEPROM Wait state Counter

Replaces the RWAIT count in the EEPROM register. The same formulas that apply to RWAIT apply

to EWAIT in the EEPROM bank.

15-0 Reserved 0 Reads return 0. Writes have no effect.

Loading...

Loading...