DCAN Control Registers

www.ti.com

1478

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

27.17.23 IF1/IF2 Command Registers (DCAN IF1CMD, DCAN IF2CMD)

The IF1/IF2 Command Register configure and Initiate the transfer between the IF1/IF2 Register sets and

the Message RAM. It is configurable which portions of the message object should be transferred.

A transfer is started when the CPU writes the message number to bits [7:0] of the IF1/IF2 Command

Register. With this write operation, the Busy bit is automatically set to 1 to indicate that a transfer is in

progress.

After 4 to 14 VBUS clock cycles, the transfer between the Interface Register and the Message RAM will

be completed and the Busy bit is cleared. The maximum number of cycles is needed when the message

transfer concurs with a CAN message transmission, acceptance filtering, or message storage.

If the CPU writes to both IF1/IF2 Command Registers consecutively (request of a second transfer while

first transfer is still in progress), the second transfer will start after the first one has been completed.

NOTE: While Busy bit is one, IF1/IF2 Register sets are write protected.

For debug support, the auto clear functionality of the IF1/IF2 Command Registers (clear of

DMAactive flag by r/w) is disabled during Debug/Suspend mode.

If an invalid Message Number is written to bits [7:0] of the IF1/IF2 Command Register, the

Message Handler may access an implemented (valid) message object instead.

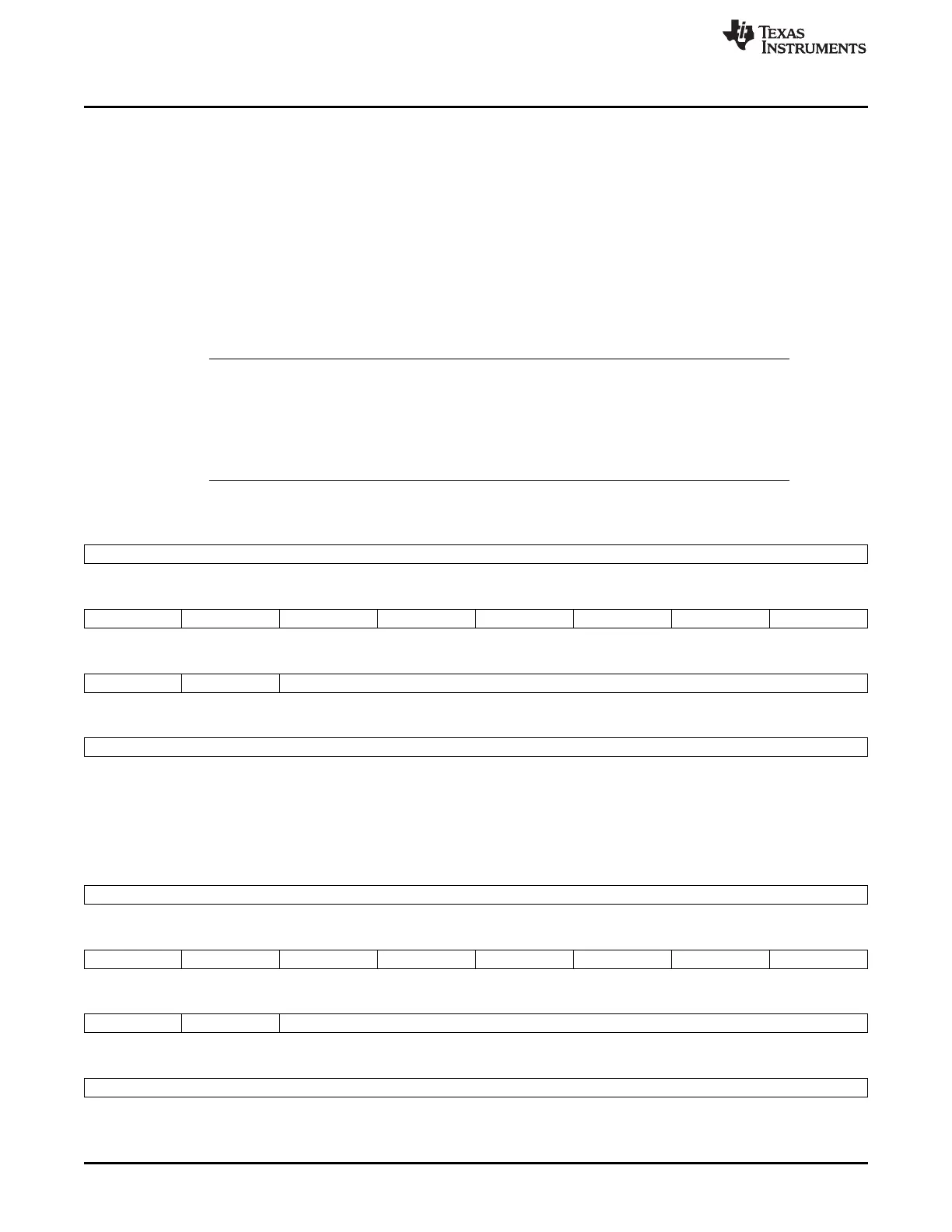

Figure 27-57. IF1 Command Registers (DCAN IF1CMD) [offset = 100h]

31 24

Reserved

R-0

23 22 21 20 19 18 17 16

WR/RD Mask Arb Control ClrIntPnd TxRqst/NewDat Data A Data B

R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0

15 14 13 8

Busy DMA Active Reserved

R-0 R/WP/C-0 R-0

7 0

Message Number

R/WP-1h

LEGEND: R/W = Read/Write; R = Read; WP = Protected Write (protected by Busy bit); C = Clear by IF1 Access; -n = value after reset

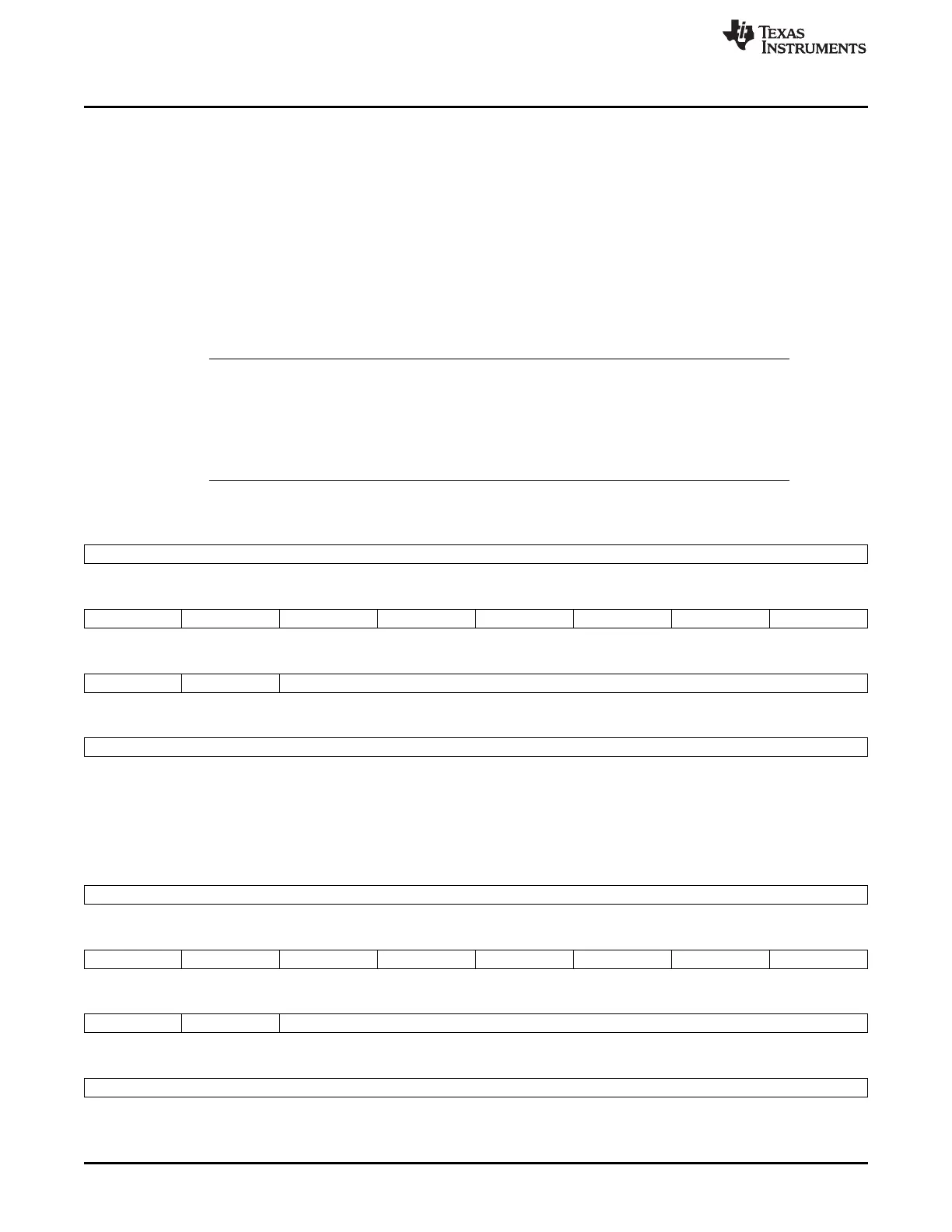

Figure 27-58. IF2 Command Registers (DCAN IF2CMD) [offset = 120h]

31 24

Reserved

R-0

23 22 21 20 19 18 17 16

WR/RD Mask Arb Control ClrIntPnd TxRqst/NewDat Data A Data B

R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0

15 14 13 8

Busy DMA Active Reserved

R-0 R/WP/C-0 R-0

7 0

Message Number

R/WP-1h

LEGEND: R/W = Read/Write; R = Read; WP = Protected Write (protected by Busy bit); C = Clear by IF1 Access; -n = value after reset

Loading...

Loading...