www.ti.com

DCAN Control Registers

1479

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

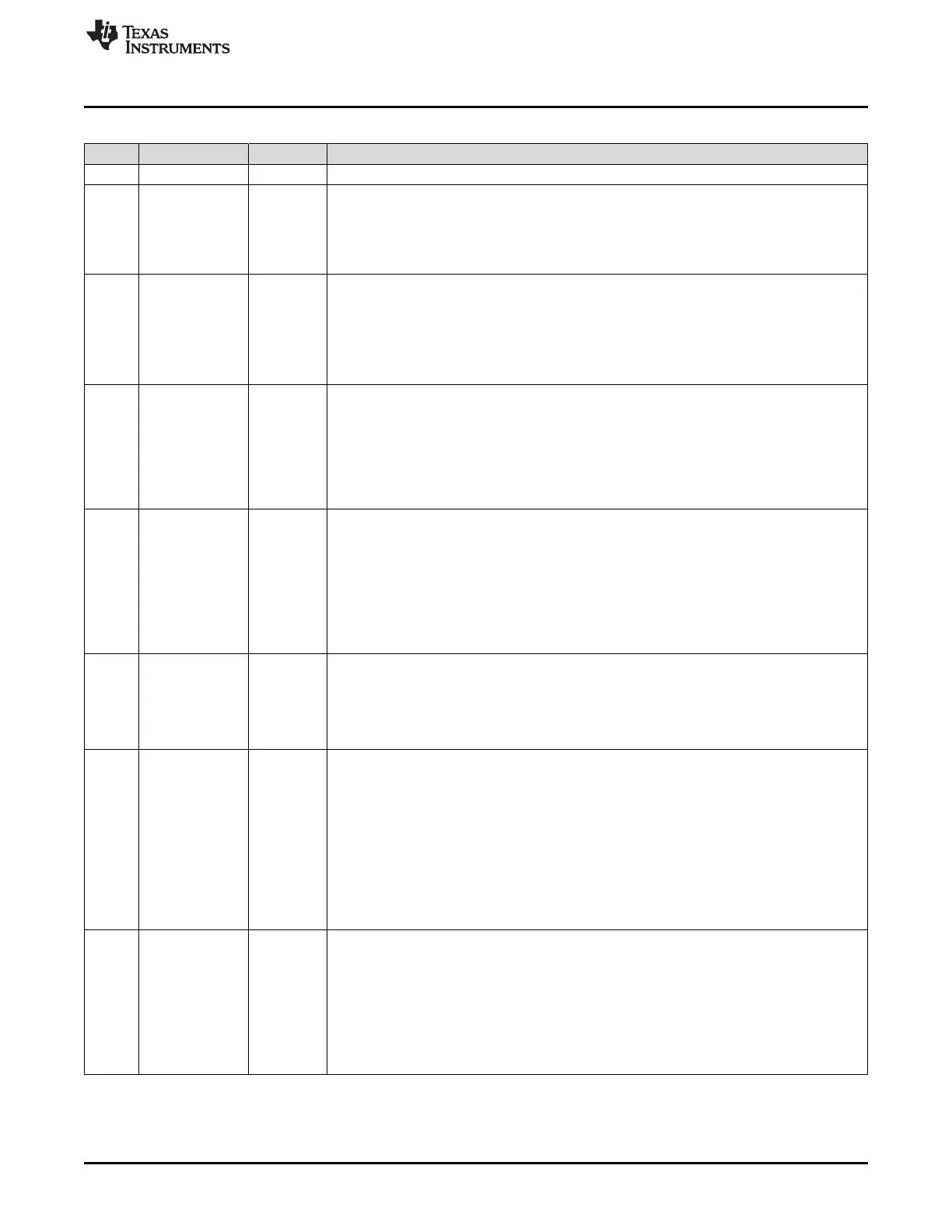

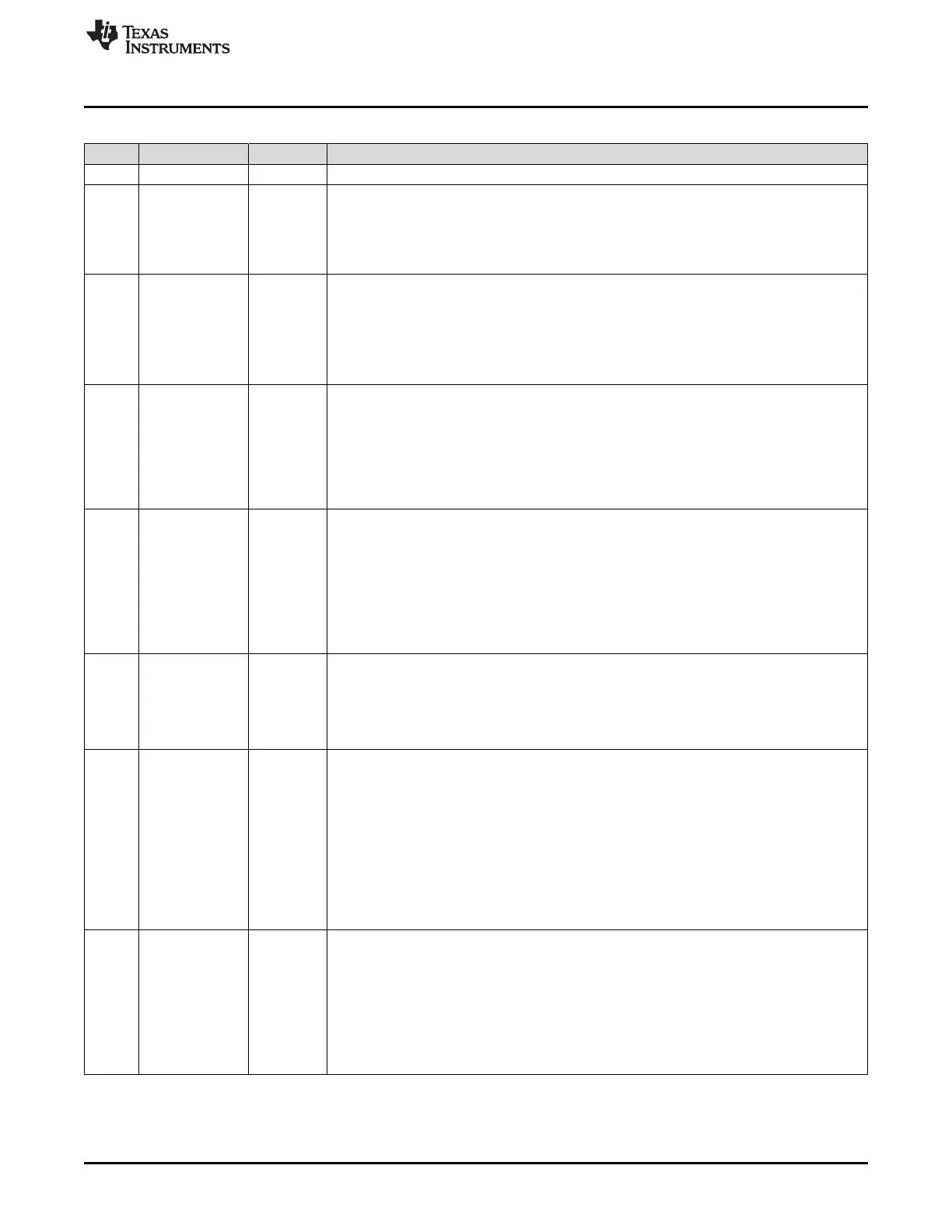

Table 27-25. IF1/IF2 Command Register Field Descriptions

Bit Field Value Description

31-24 Reserved 0 These bits are always read as 0. Writes have no effect.

23 WR/RD Write/Read

0 Direction = Read: Transfer direction is from the message object addressed by Message

Number (Bits [7:0]) to the IF1/IF2 register set.

1 Direction = Write: Transfer direction is from the IF1/IF2 register set to the message object

addressed by Message Number (Bits [7:0]).

22 Mask Access Mask bits.

0 Mask bits will not be changed.

1 Direction = Read: The Mask bits (Identifier Mask + MDir + MXtd) will be transferred from the

message object addressed by Message Number (Bits [7:0]) to the IF1/IF2 Register set.

Direction = Write: The Mask bits (Identifier Mask + MDir + MXtd) will be transferred from the

IF1/IF2 Register set to the message object addressed by Message Number (Bits [7:0]).

21 Arb Access Arbitration bits.

0 Arbitration bits will not be changed.

1 Direction = Read: The Arbitration bits (Identifier + Dir + Xtd + MsgVal) will be transferred from

the message object addressed by Message Number (Bits [7:0]) to the corresponding IF1/IF2

Register set.

Direction = Write: The Arbitration bits (Identifier + Dir + Xtd + MsgVal) will be transferred from

the IF1/IF2 Register set to the message object addressed by Message Number (Bits [7:0]).

20 Control Access Control bits.

0 Control bits will not be changed.

1 Direction = Read: The Message Control bits will be transferred from the message object

addressed by Message Number (Bits [7:0]) to the corresponding IF1/IF2 Register set.

Direction = Write: The Message Control bits will be transferred from the IF1/IF2 Register set to

the message object addressed by Message Number (Bits [7:0]).

If the TxRqst/NewDat bit in this register (Bit [18]) is set, the TxRqst/NewDat bit in the IF1/IF2

Message Control Register will be ignored.

19 ClrIntPnd Clear Interrupt Pending bit.

0 IntPnd bit will not be changed.

1 Direction = Read: Clears IntPnd bit in the message object.

Direction = Write: This bit is ignored. Copying of IntPnd flag from IF1/IF2 Registers to Message

RAM can be controlled by only the Control flag (Bit [20]).

18 TxRqst/NewDat Access Transmission Request bit.

0 Direction = Read: NewDat bit will not be changed.

Direction = Write: TxRqst/NewDat bit will be handled according to the Control bit.

1 Direction = Read: Clears NewDat bit in the message object.

Direction = Write: Sets TxRqst/NewDat in the message object.

Note: If a CAN transmission is requested by setting TxRqst/NewDat in this register, the

TxRqst/NewDat bits in the message object will be set to 1 and independent of the values in

IF1/IF2 Message Control Register.

A read access to a message object can be combined with the reset of the control bits IntPnd

and NewDat. The values of these bits transferred to the IF1/IF2 Message Control Register

always reflect the status before resetting them.

17 Data A Access Data Bytes 0–3.

0 Data Bytes 0–3 will not be changed.

1 Direction = Read: The Data Bytes 0–3 will be transferred from the message object addressed

by the Message Number (Bits [7:0]) to the corresponding IF1/IF2 Register set.

Direction = Write: The Data Bytes 0–3 will be transferred from the IF1/IF2 Register set to the

message object addressed by the Message Number (Bits [7:0]).

Note: The duration of the message transfer is independent of the number of bytes to be

transferred.

Loading...

Loading...