www.ti.com

DCAN Control Registers

1465

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

27.17.7 Parity Error Code Register (DCAN PERR)

If a double-bit error is detected, the PER flag will be set in the Error and Status Register. This bit is not

reset by the SECDED mechanism; it must be reset by reading the Error and Status Register. In addition to

the PER flag, the SECDED Error Code Register will indicate the memory area where the double-bit error

has been detected (message number). After a double-bit error has been detected, the register will hold the

last error code until power is removed.

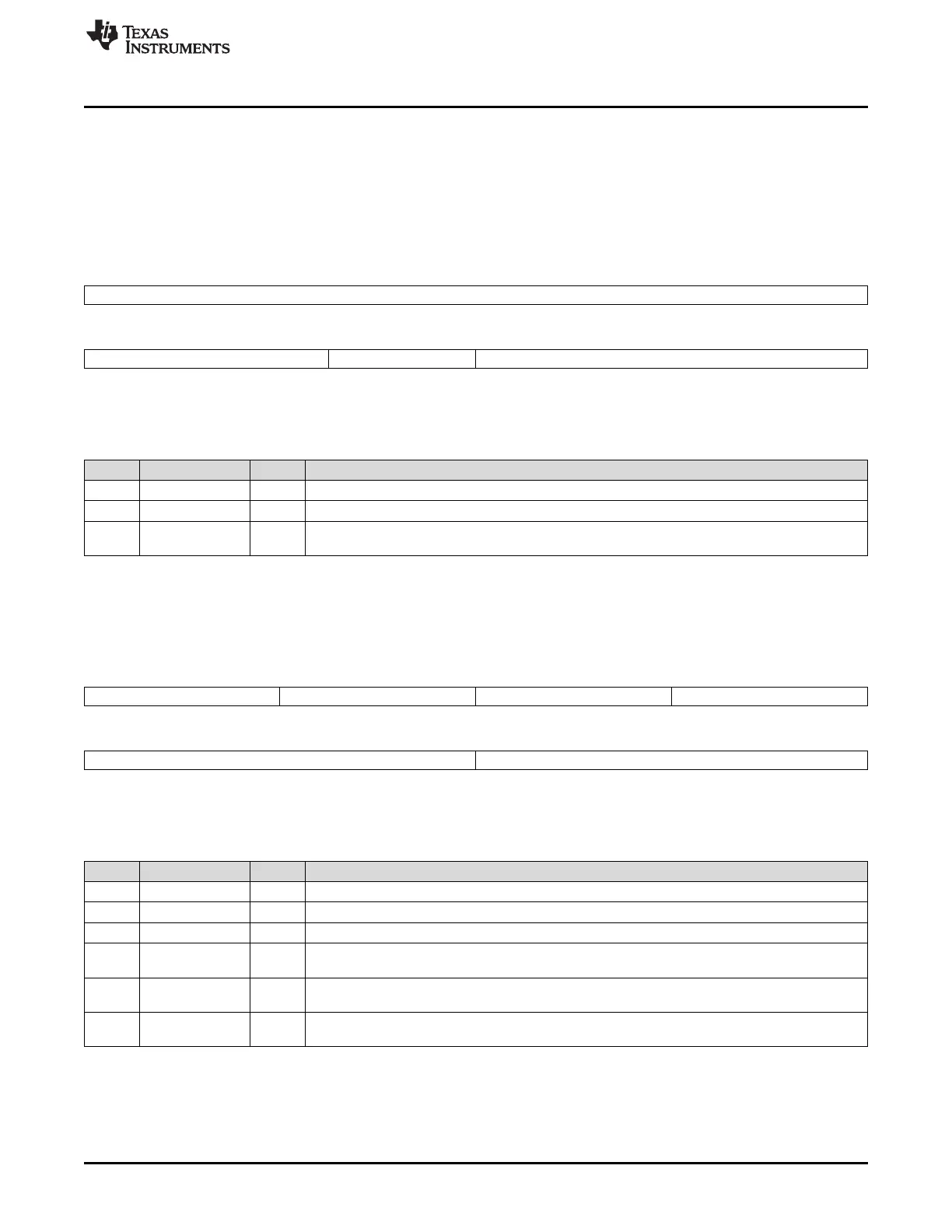

Figure 27-26. Parity Error Code Register (DCAN PERR) [offset = 1Ch]

31 16

Reserved

R-0

15 14 11 10 8 7 0

Reserved Word Number Message Number

R-0 R-U R-U

LEGEND: R = Read only; U = value is undefined; -n = value after reset

Table 27-13. Parity Error Code Register (DCAN PERR) Field Descriptions

Bit Field Value Description

31-11 Reserved 0 These bits are always read as 0. Writes have no effect.

10-8 Word Number 0 Word Number is reserved and it will always read as 0.

7-0 Message Number 1h-FFh Message object number where double-bit error has been detected. Only values 1h-40h are valid.

Values 41h-FFh are invalid.

27.17.8 Core Release Register (DCAN REL)

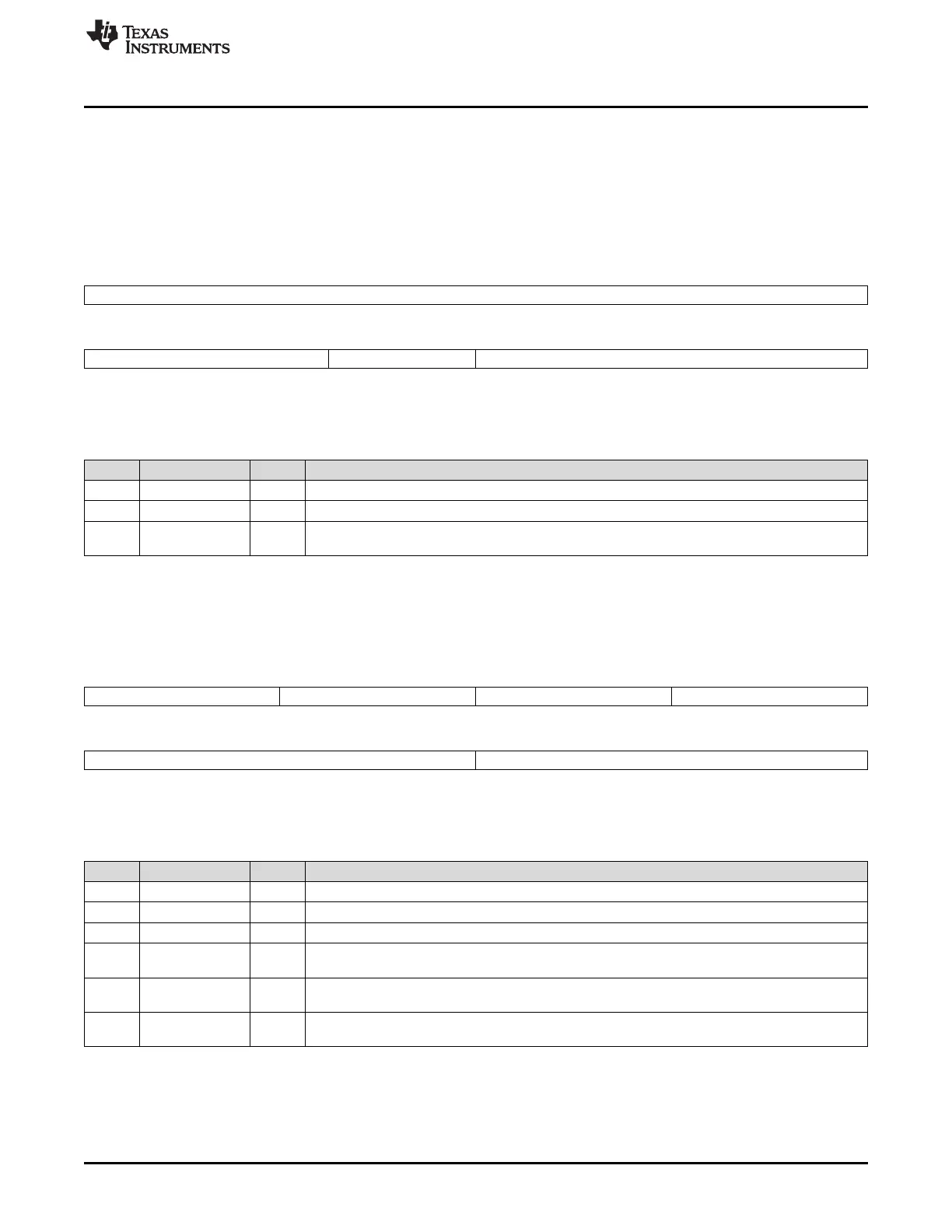

Figure 27-27. Core Release Register (DCAN REL) [offset = 20h]

31 28 27 24 23 20 19 16

REL STEP SUBSTEP YEAR

R-Ah R-3h R-1h R-7h

15 8 7 0

MON DAY

R-5h R-4h

LEGEND: R = Read only; -n = value after reset

Table 27-14. Core Release Register (DCAN REL) Field Descriptions

Bit Field Value Description

31-28 REL 0-9h Core Release. One digit, BCD-coded.

27-24 STEP 0-9h Step of Core Release. One digit, BCD-coded.

23-20 SUBSTEP 0-9h Substep of Core Release. One digit, BCD-coded.

19-16 YEAR 0-9h Design Time Stamp, Year. One digit, BCD-coded. This field is set by constant parameter on DCAN

synthesis.

15-8 MON 0-12h Design Time Stamp, Month. Two digits, BCD-coded. This field is set by constant parameter on

DCAN synthesis.

7-0 DAY 0-31h Design Time Stamp, Day. Two digits, BCD-coded. This field is set by constant parameter on DCAN

synthesis.

Loading...

Loading...