DCAN Control Registers

www.ti.com

1464

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

27.17.6 Test Register (DCAN TEST)

For all test modes, the Test bit in CAN Control Register needs to be set to one. If Test bit is set, the RDA,

EXL, Tx1, Tx0, LBack and Silent bits are writable. Bit Rx monitors the state of pin CAN_RX and therefore

is only readable. All Test Register functions are disabled when Test bit is cleared.

NOTE: The Test Register is only writable if Test bit in CAN Control Register is set.

Setting Tx[1:0] other than 00 will disturb message transfer.

When the internal loop back mode is active (bit LBack is set), bit EXL will be ignored.

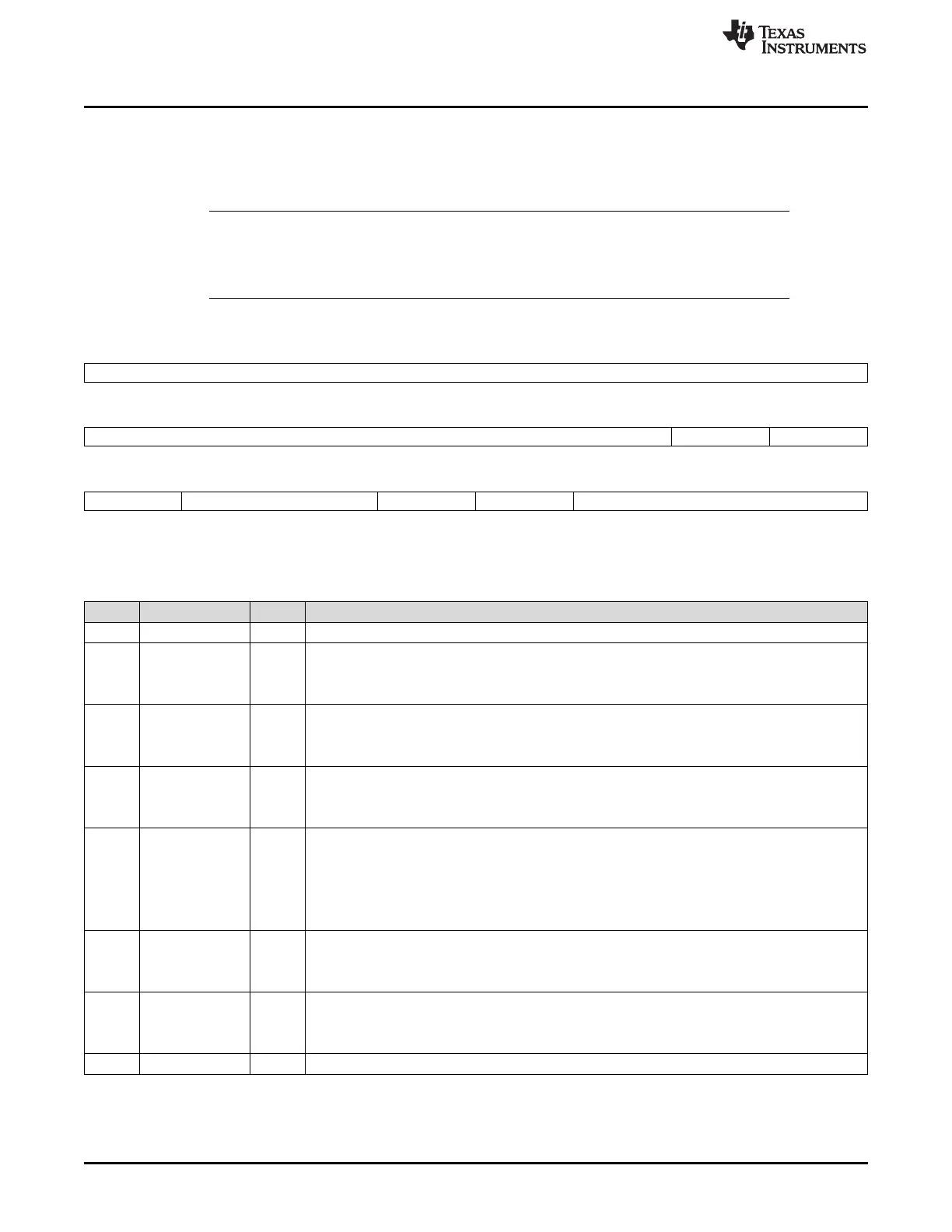

Figure 27-25. Test Register (DCAN TEST) [offset = 14h]

31 16

Reserved

R-0

15 10 9 8

Reserved RDA EXL

R-0 R/WP-0 R/WP-0

7 6 5 4 3 2 0

Rx Tx LBack Silent Reserved

R-U R/WP-0 R/WP-0 R/WP-0 R-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write Protected by Test bit; -n = value after reset; U = Undefined

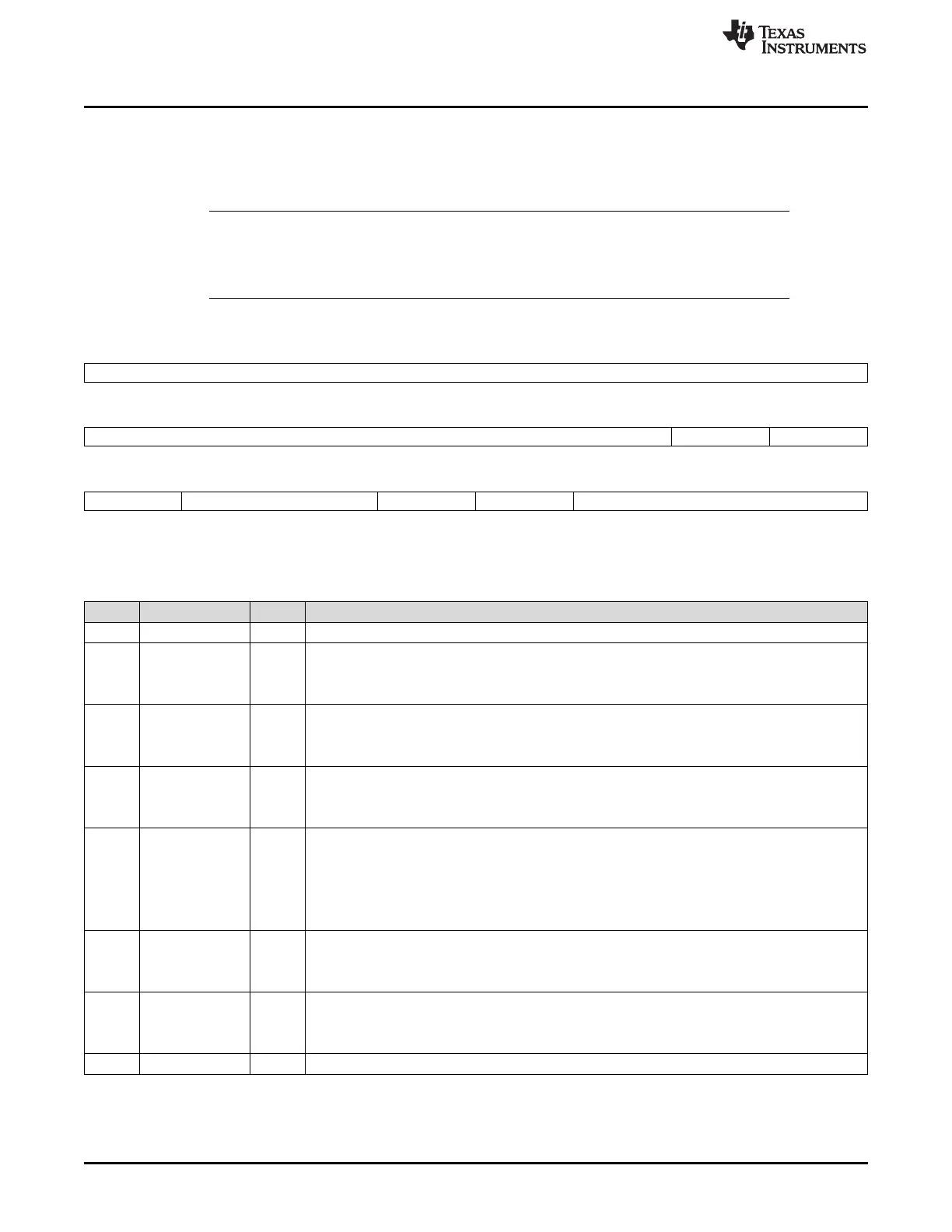

Table 27-12. Test Register (DCAN TEST) Field Descriptions

Bit Field Value Description

31-10 Reserved 0 These bits are always read as 0. Writes have no effect.

9 RDA RAM direct access enable.

0 Normal operation.

1 Direct access to the RAM is enabled while in Test Mode.

8 EXL External loop back mode.

0 Disabled

1 Enabled

7 Rx Receive Pin. Monitors the actual value of the CAN_RX pin.

0 The CAN bus is dominant.

1 The CAN bus is recessive.

6-5 Tx Control of CAN_TX pin.

0 Normal operation, CAN_TX is controlled by the CAN Core.

1h Sample Point can be monitored at CAN_TX pin.

2h CAN_TX pin drives a dominant value.

3h CAN_TX pin drives a recessive value.

4 LBack Loop back mode.

0 Disabled

1 Enabled

3 Silent Silent mode.

0 Disabled

1 Enabled

2-0 Reserved 0 These bits are always read as 0. Writes have no effect.

Loading...

Loading...