www.ti.com

Message Interface Register Sets

1435

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

27.6.3 Message Interface Register 3

The IF3 register set can automatically be updated with received message objects without the need to

initiate the transfer from Message RAM by CPU. The intention of this feature of IF3 is to provide an

interface for the DMA to read packets efficiently.

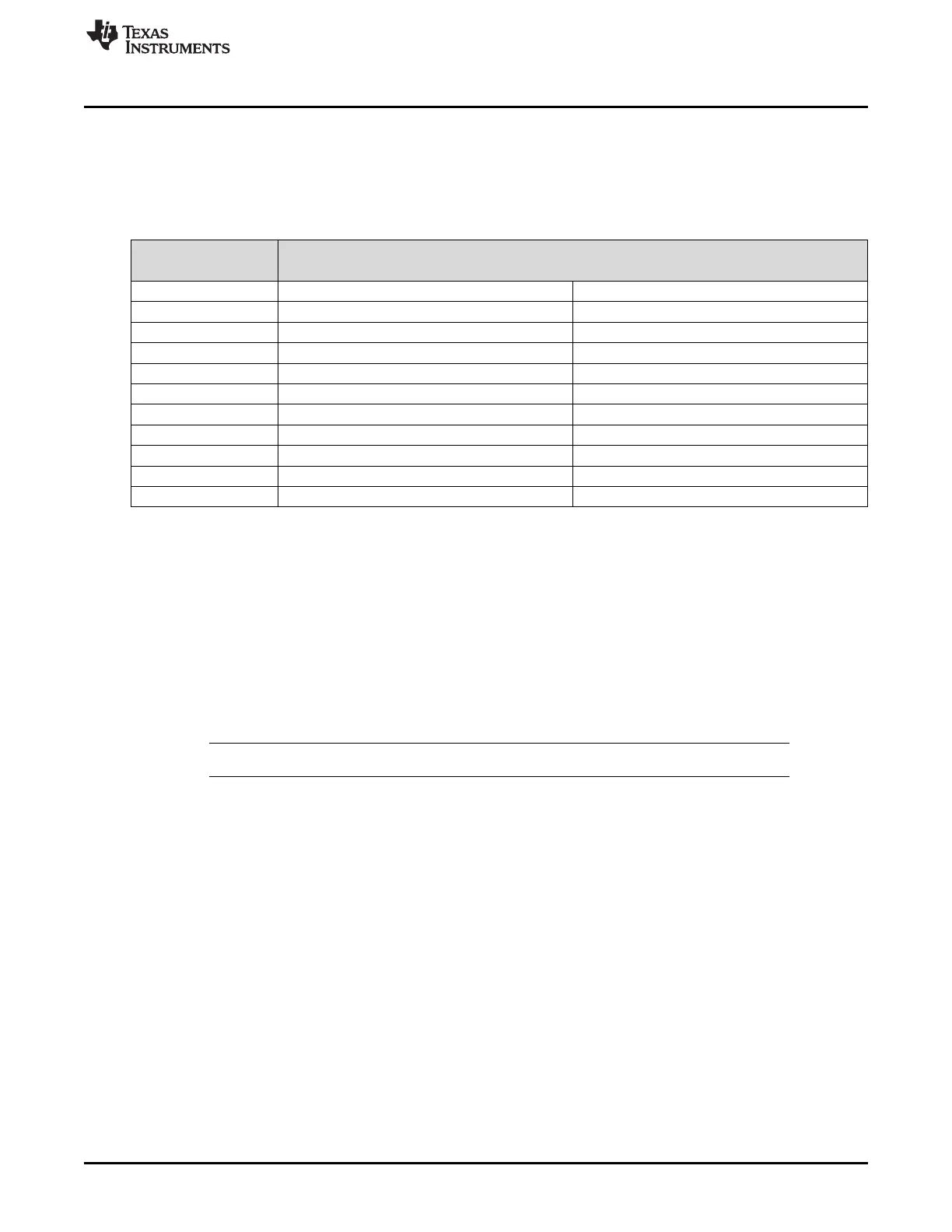

Table 27-5. Message Interface Register 3

Address IF3 Register Set

[CAN Base +] 31 16 15 0

0x140 reserved IF3 Observation

0x144 IF3 Mask 2 IF3 Mask 1

0x148 IF3 Arbitration 2 IF3 Arbitration 1

0x14C reserved IF3 Message Control

0x150 IF3 Data A 2 IF3 Data A 1

0x154 IF3 Data B 2 IF3 Data B 1

: : :

0x160 IF3 Update Enable 2 IF3 Update Enable 1

0x164 IF3 Update Enable 4 IF3 Update Enable 3

0x168 IF3 Update Enable 6 IF3 Update Enable 5

0x16C IF3 Update Enable 8 IF3 Update Enable 7

The automatic update functionality can be programmed for each message object (see IF3 Update Enable

Register, Section 27.17.33).

All valid message objects in Message RAM that are configured for automatic update, will be checked for

active NewDat flags. If such a message object is found, it will be transferred to the IF3 register (if no

previous DMA transfers are ongoing), controlled by IF3 Observation register. If more than one NewDat

flag is active, the message object with the lowest number has the highest priority for automatic IF3 update.

The NewDat bit in the message object will be reset by a transfer to IF3.

If DCAN internal IF3 update is complete, a DMA request is generated. The DMA request stays active until

first read access to one of the IF3 registers. The DMA functionality has to be enabled by setting bit DE3 in

CAN Control register. Please refer to the device datasheet to find out if this DMA source is available.

NOTE: The IF3 register set can not be used for transferring data into message objects.

Loading...

Loading...