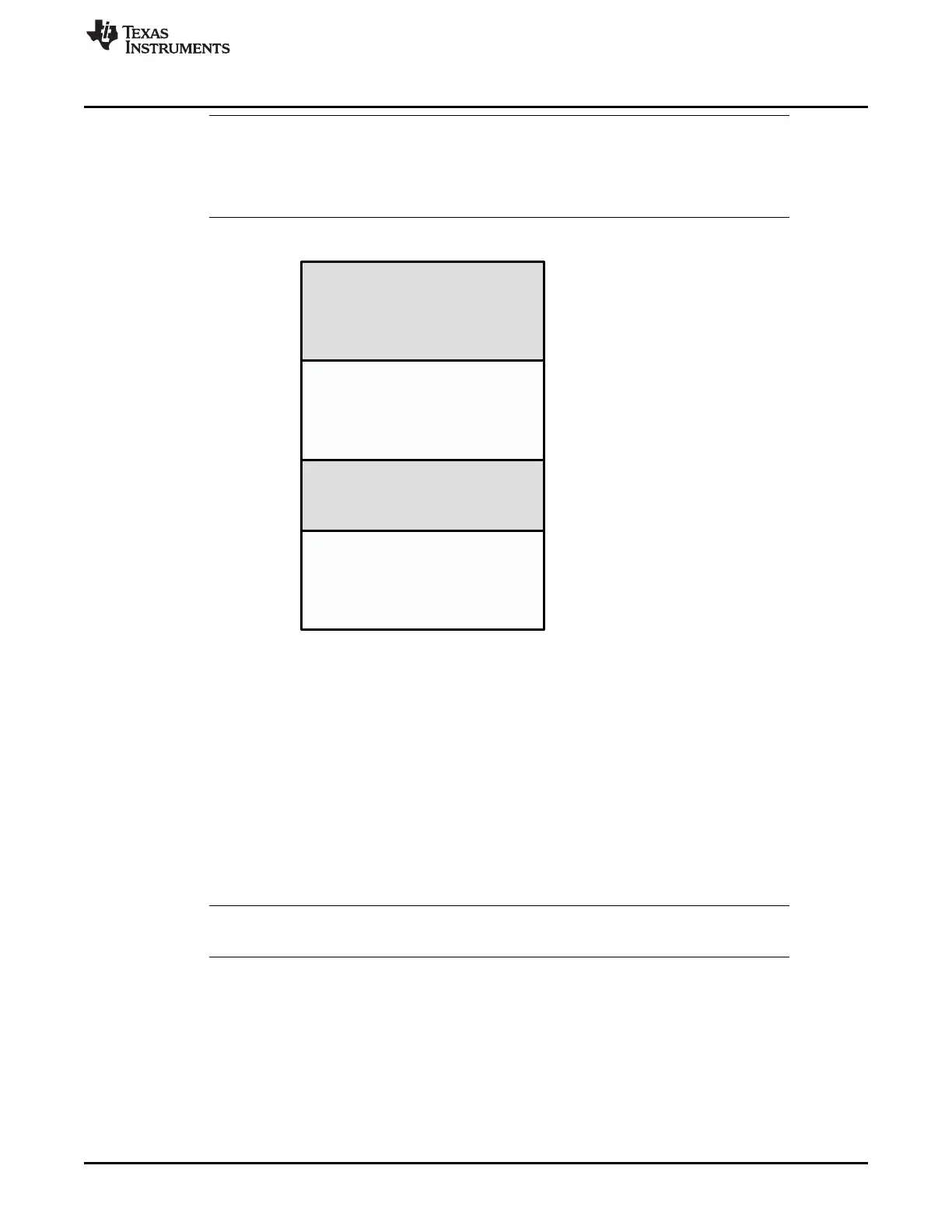

Implemented data space

Implemented ECC space

Illegal address

8 MB

4MB

4MB + 512KB

512KB

0x0

Illegal address

www.ti.com

Module Operation

389

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Level 2 RAM (L2RAMW) Module

NOTE: No ECC Error Generated for Accesses to ECC Memory: A read from the ECC memory

itself would generate an ECC value on both the read data bus as well as the 8-bit ECC bus.

This could result in the detection of a multi-bit error by the SECDED logic inside the CPU.

The L2RAMW interface module ignores the ECC errors that are indicated by the CPU when

accessing ECC space.

Figure 8-1. RAM Memory Map

8.2.2 Safety Features

The L2RAMW module incorporates some features that are designed specifically with safety

considerations.

8.2.2.1 ECC Handling on 8-, 16-, and 32-Bit Writes

ECC calculation is handled by the R5F CPU except in the case of sub-64bit writes. If an 8-, 16-, or a 32-

bit write is performed, L2RAMW handles the ECC calculation along with read-modify-write operation. This

is to minimize the latency between CPU and L2RAMW in the case of sub-64bit write.

When a sub-64 bit write is performed with ECC enabled, the RAM Error Status Register flags any errors

that are detected by the ECC logic of the L2RAMW.

NOTE: The RAM Error Status Register does not indicate ECC errors that are detected by the Cortex

R5F CPU. These errors and handled and flagged in the R5F registers

Loading...

Loading...