Control Registers and Control Packets

www.ti.com

724

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Direct Memory Access Controller (DMA) Module

20.3.1 Global Configuration Registers

These registers control the overall behavior of the DMA controller.

20.3.1.1 Global Control Register (GCTRL)

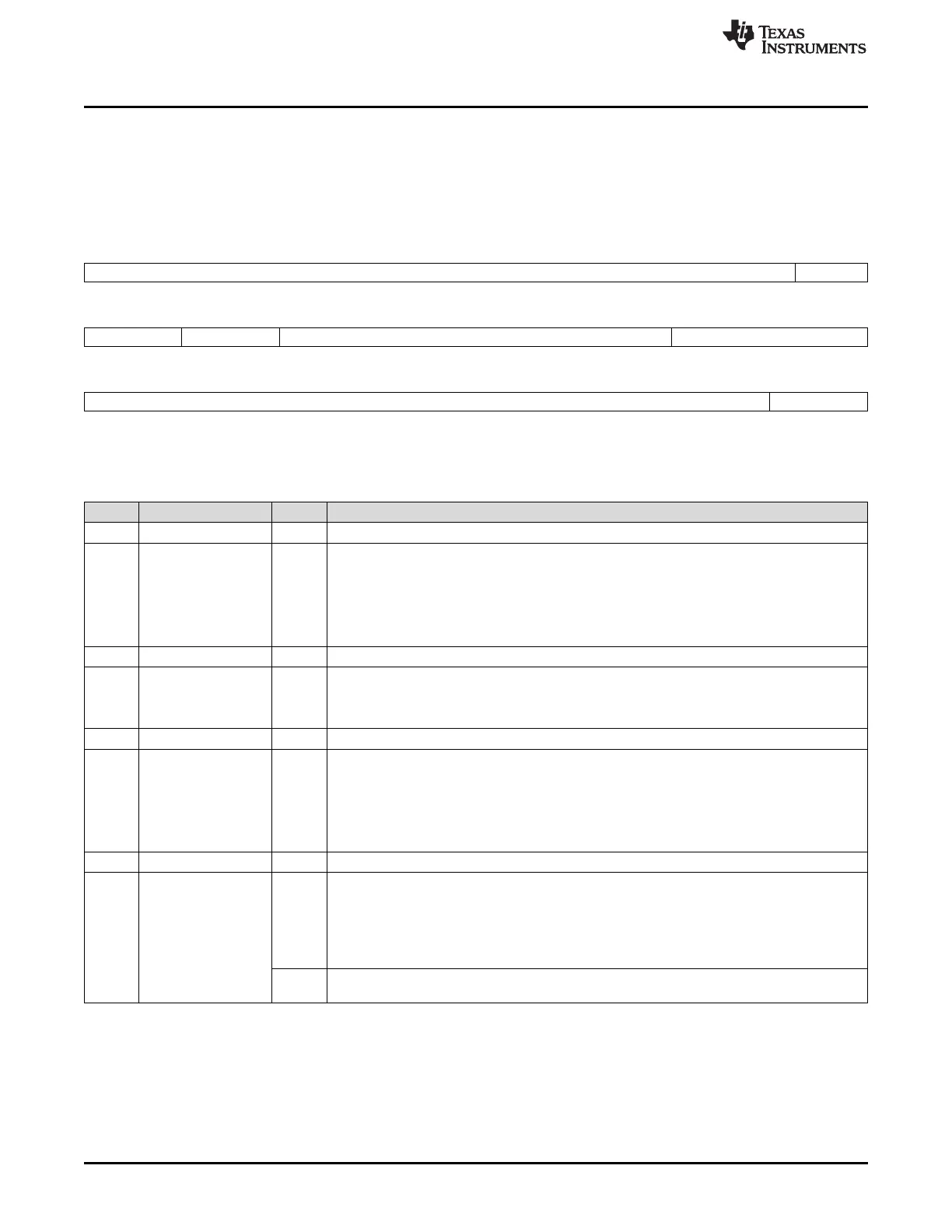

Figure 20-19. Global Control Register (GCTRL) [offset = 00]

31 17 16

Reserved DMA_EN

R-0 R/WP-0

15 14 13 10 9 8

Reserved BUS_BUSY Reserved DEBUGMODE

R-0 R-0 R-0 R/WP-0

7 1 0

Reserved DMARES

R-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privilege mode only; -n = value after reset

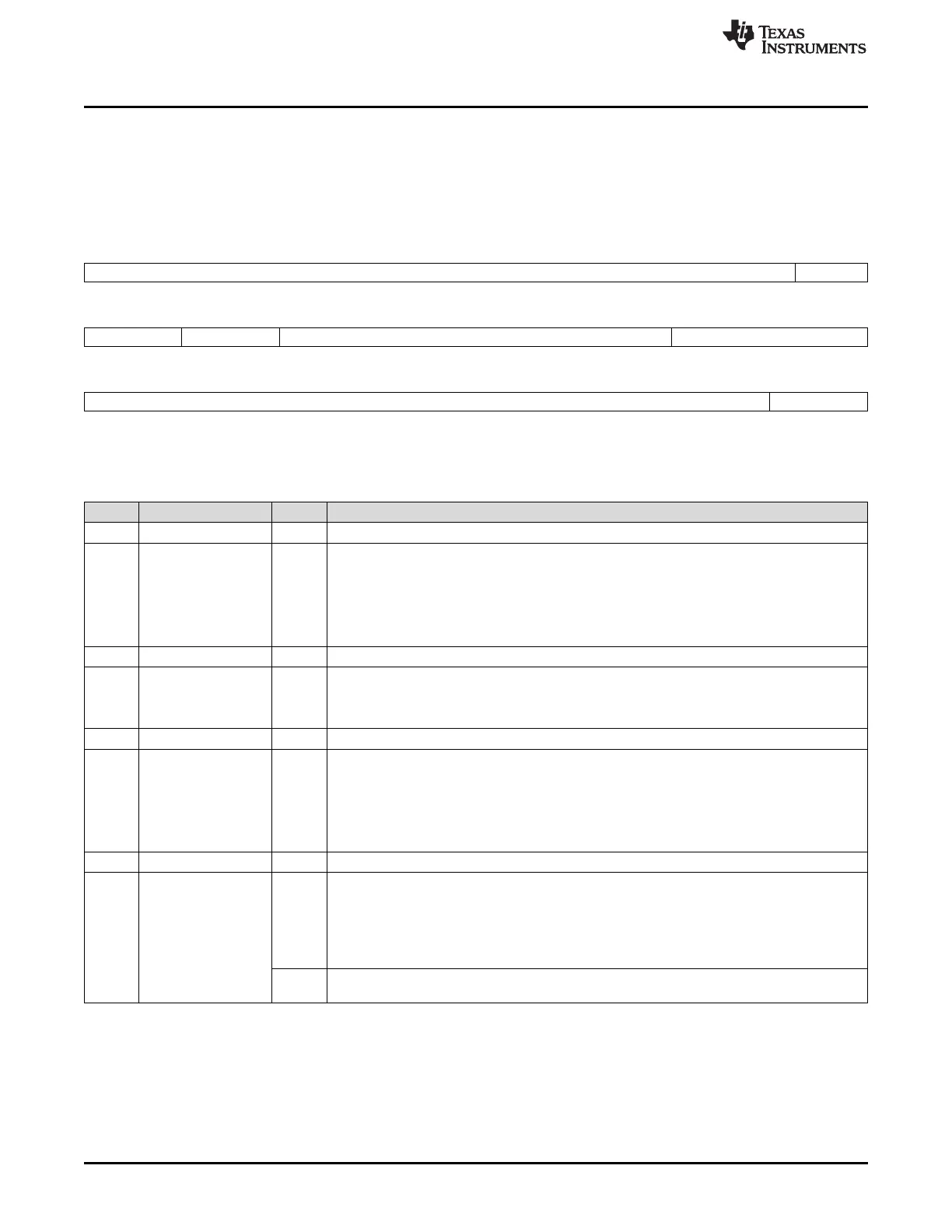

Table 20-9. Global Control Register (GCTRL) Field Descriptions

Bit Field Value Description

31-17 Reserved 0 Reads return 0. Writes have no effect.

16 DMA_EN DMA enable bit. The configuration registers and channel control packets should be setup first

before DMA_EN bit is set to one to prevent state machines from carrying out bus transactions.

If DMA_EN bit is cleared in the middle of an bus transaction, the state machine will stop at an

arbitration boundary.

0 The DMA is disabled.

1 The DMA is enabled.

15 Reserved 0 Reads return 0. Writes have no effect.

14 BUS_BUSY This bit indicates status of DMA external AHB bus status.

0 DMAs external bus is not busy in data transfers.

1 DMAs external bus is busy in data transfers.

13-10 Reserved 0 Reads return 0. Writes have no effect.

9-8 DEBUGMODE Debug Mode.

0 Ignore suspend.

1h Finish current block transfer.

2h Finish current frame transfer.

3h Immediately stop at an DMA arbitration boundary and continue after suspend.

7-1 Reserved 0 Reads return 0. Writes have no effect.

0 DMARES DMA software reset.

Note: In the event a DMA slave does not respond, the DMA module will respond to the

software reset upon reaching an arbitration boundary.

0 Read: Software reset is disabled.

Write: No effect.

1 Read and write: The DMA state machine and all control registers are in software reset. Control

packets are not reset when DMA software reset is active.

Loading...

Loading...