SDC MMR Registers

www.ti.com

278

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Interconnect

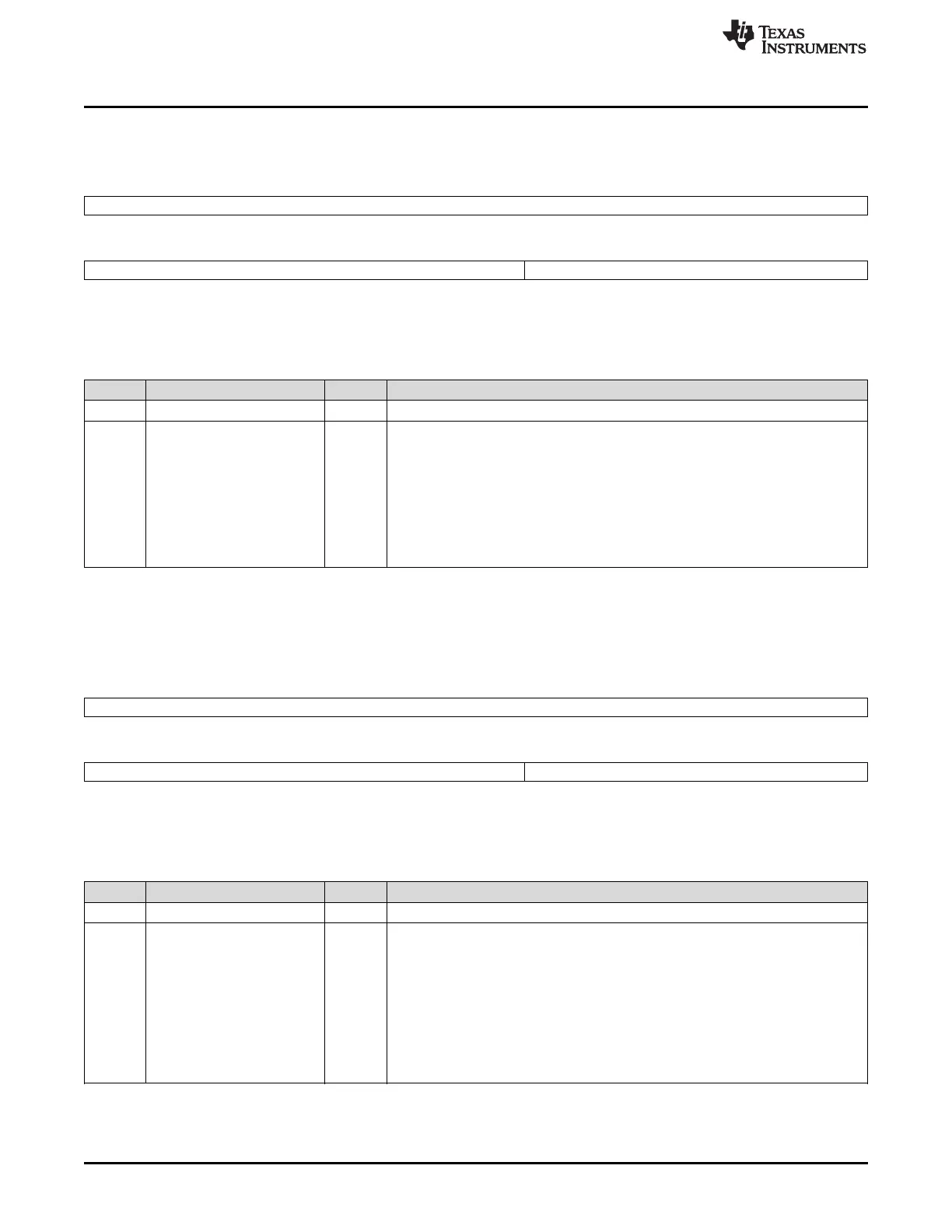

4.4.10 Slave Error Address Decode Register (SERR_ADDR_DECODE)

Figure 4-11. Slave Error Address Decode Register (SERR_ADDR_DECODE) (offset = 24h)

31 16

Reserved

R-0

15 7 6 0

Reserved SERR_ADDR_DECODE

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 4-15. Slave Error Address Decode Register (SERR_ADDR_DECODED) Field Descriptions

Bit Field Value Description

31-7 Reserved 0 Reads return 0 and writes have no effect.

6-0 SERR_ADDR_ DECODE Error related to mismatch on the most-significant address bits. When set, each bit

indicates the transaction processing block inside the interconnect corresponding to

the slave that is detected by the interconnect checker to have a fault.

bit 0: L2 SRAM slave

bit 1: L2 Flash PortB slave

bit 2: L2 Flash PortA slave

bit 3: EMIF slave

bit 4: Reserved

bit 5: Cortex-R5F CPU AXI slave

bit 6: ACP-S slave

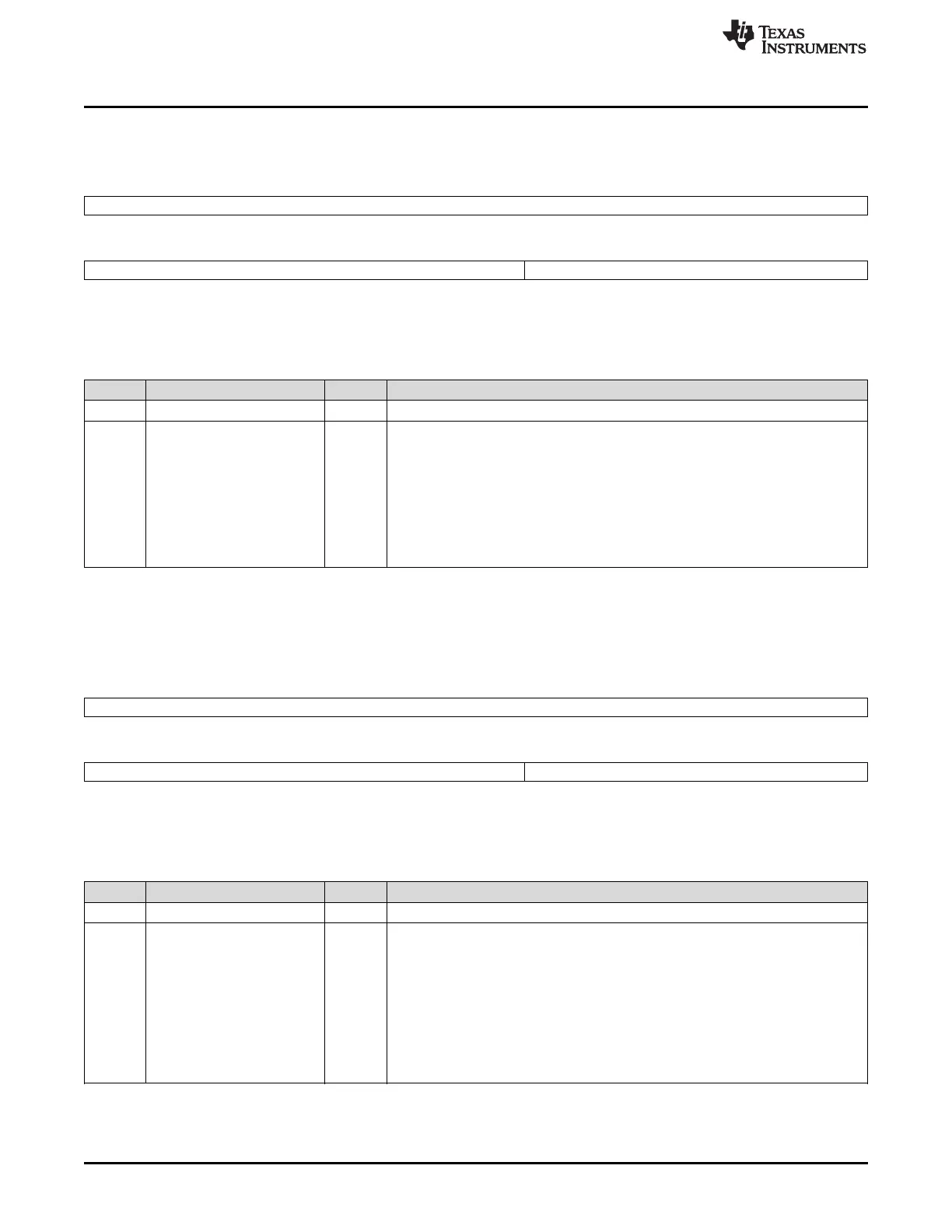

4.4.11 Slave Error User Parity Register (SERR_USER_PARITY)

Figure 4-12. Slave Error User Parity Register (SERR_USER_PARITY) (offset = 28h)

31 16

Reserved

R-0

15 7 6 0

Reserved SERR_USER_PARITY

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 4-16. Slave Error User Parity Register (SERR_USER_PARITYID) Field Descriptions

Bit Field Value Description

31-7 Reserved 0 Reads return 0 and writes have no effect.

6-0 SERR_USER_PARITY Error related to mismatch on the parity on the response signals for the slave. When

set, each bit indicates the transaction processing block inside the interconnect

corresponding to the slave that is detected by the interconnect checker to have a

fault.

bit 0: L2 SRAM slave

bit 1: L2 Flash PortB slave

bit 2: L2 Flash PortA slave

bit 3: EMIF slave

bit 4: Reserved

bit 5: Cortex-R5F CPU AXI slave

bit 6: ACP-S slave

Loading...

Loading...