www.ti.com

VIM Control Registers

683

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Vectored Interrupt Manager (VIM) Module

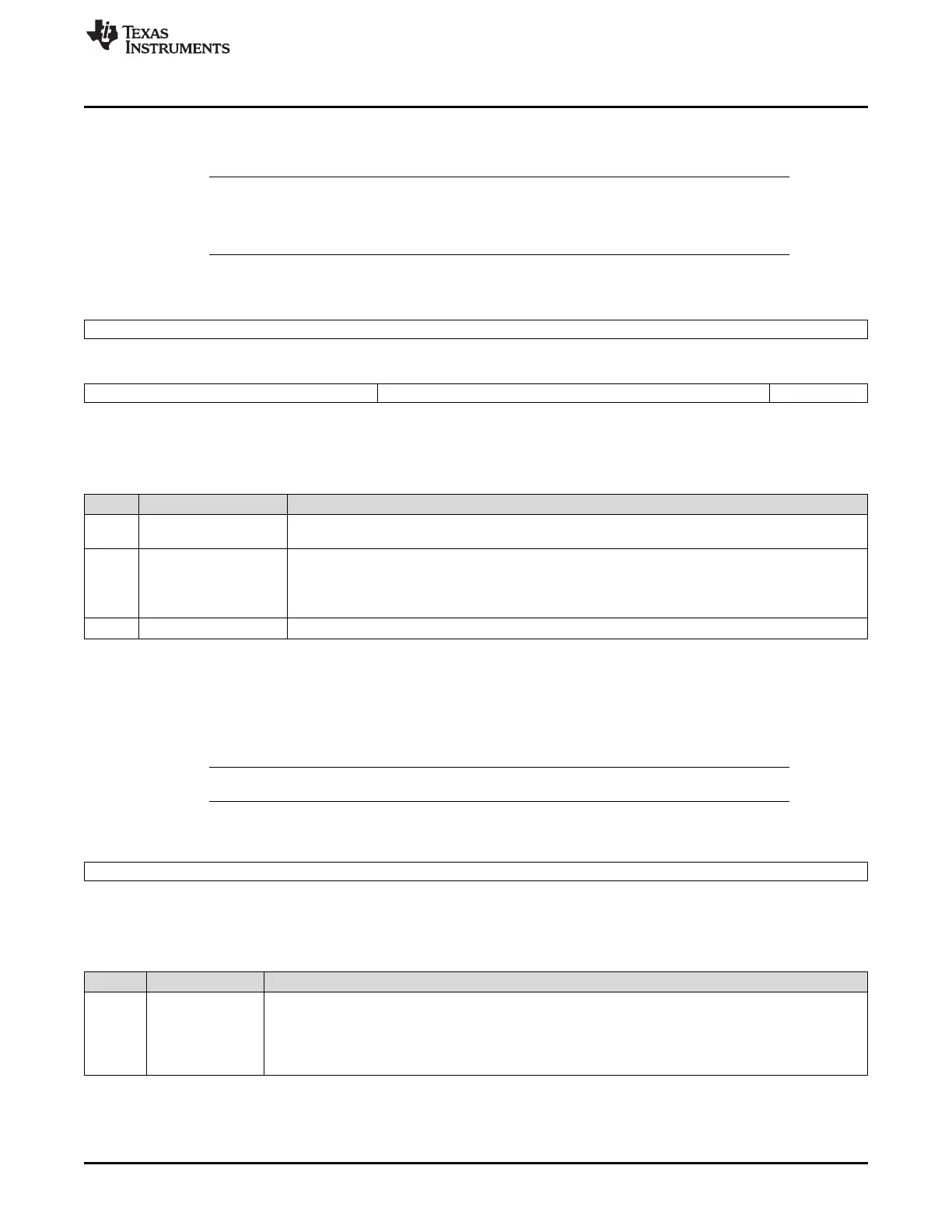

19.9.3 Uncorrectable Error Address Register (UERRADDR)

The uncorrectable error address register gives the address of the first uncorrectable error location.

NOTE: No computation is needed when reading the complete register to retrieve the address in the

Interrupt Vector Table.

This register will never be reset by a power-on reset nor any other reset source.

Figure 19-14. Uncorrectable Error Address Register (UERRADDR) [offset = F4h]

31 16

Interrupt Vector Table offset

R-FFF8h

15 10 9 2 1 0

Interrupt Vector Table offset ADDERR Word offset

R-0010 000b R-x R-0

LEGEND: R = Read only; x = value is indeterminate; -n = value after reset

Table 19-8. Uncorrectable Error Address Register (UERRADDR) Field Descriptions

Bit Field Description

31-10 Interrupt Vector Table

offset

Interrupt Vector Table offset. Reads are always FFF8 2xxxh; writes have no effect.

9-2 ADDERR Uncorrectable error address register. This register gives the address of the first encountered double-bit

error since the flag has been clear. Subsequent ECC errors will not update this register until the UERR

flag has been cleared.

Note: This register is valid only when PARFLG is set (see Section 19.9.1).

1-0 Word offset Word offset. Reads are always 0; writes have no effect.

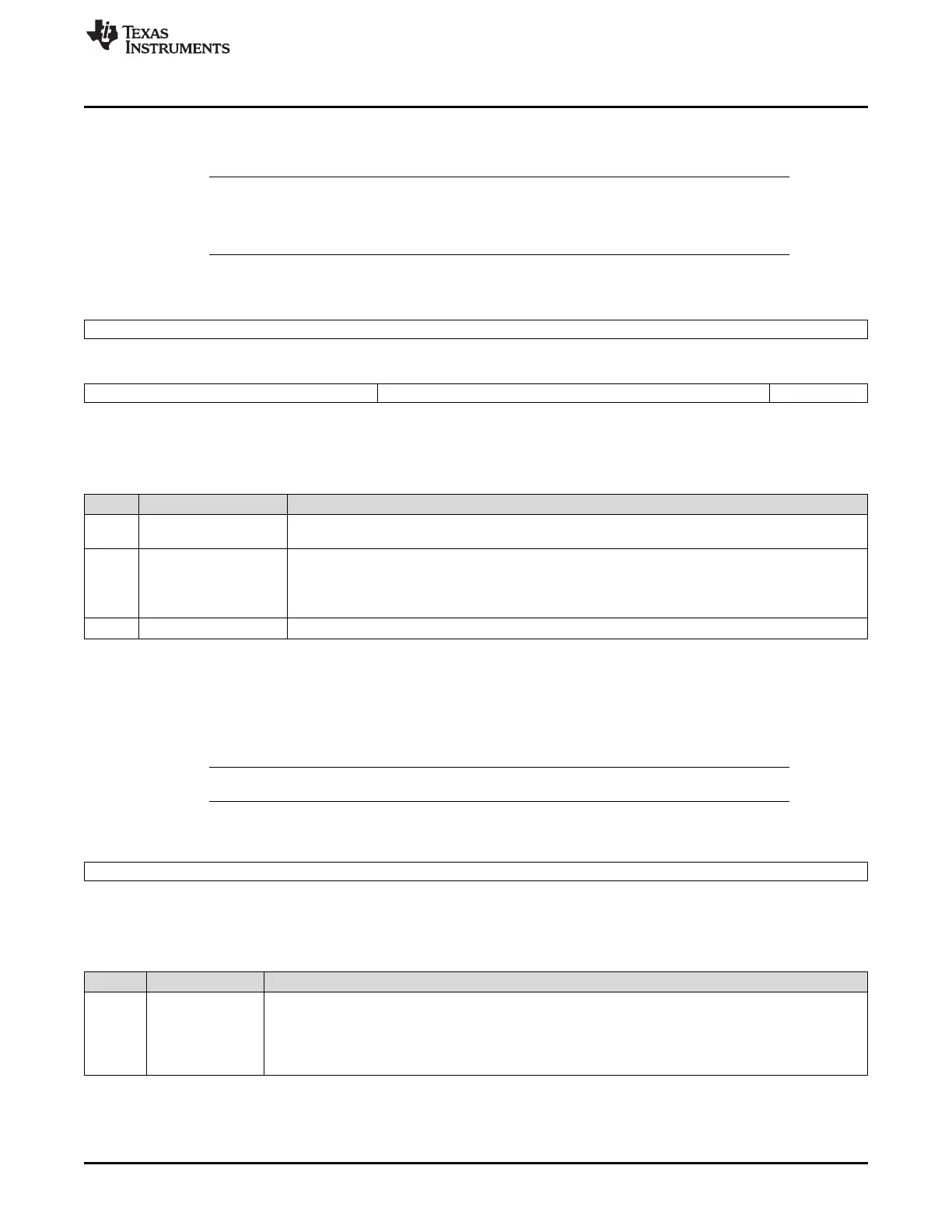

19.9.4 Fallback Vector Address Register (FBVECADDR)

This register provides a fall-back address to the VIM if a uncorrectable error has occurred in the Interrupt

Vector Table. Figure 19-15 and Table 19-9 describe this register.

NOTE: This register will never be reset by a power-on reset nor any other reset source.

Figure 19-15. Fallback Vector Address Register (FBVECADDR) [offset = F8h]

31 0

FBVECADDR

R/WP-x

LEGEND: R/W = Read/Write; WP = Write in privilege mode only; x = value is indeterminate; -n = value after reset

Table 19-9. Fallback Vector Address Register (FBVECADDR) Field Descriptions

Bit Field Description

31-0 FBVECADDR Fallback Vector Address Register. This register is used by the VIM if the Interrupt Vector Table has been

corrupted. The contents of the IRQVECREG and FIQVECREG registers will reflect the value programmed

in FBVECADDR. The value provided to the VIC port will also reflect FBVECADDR until the UERR register

has been cleared.

This register provides the address of the ISR that will restore the integrity of the Interrupt Vector Table.

Loading...

Loading...