ESM Control Registers

www.ti.com

572

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Error Signaling Module (ESM)

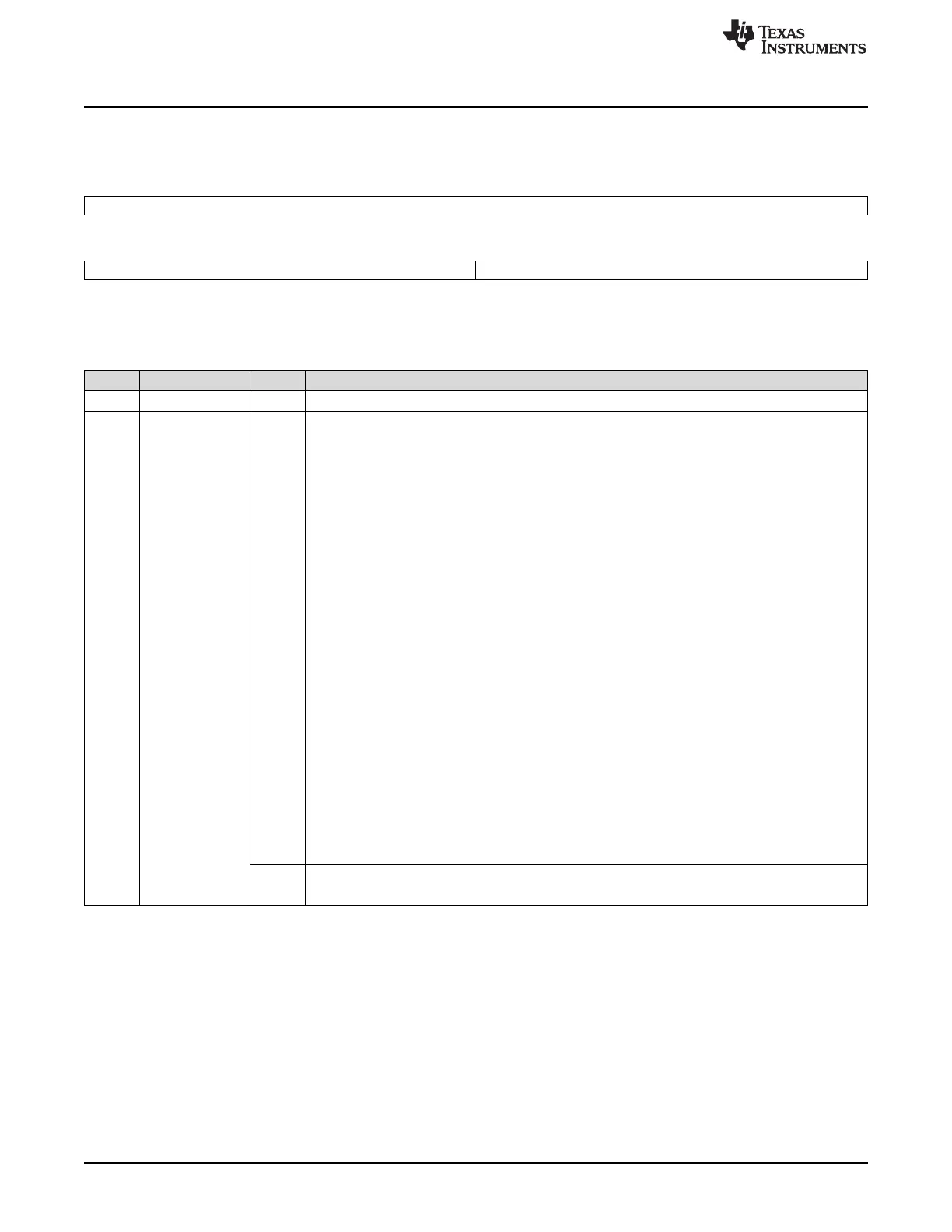

16.4.12 ESM Interrupt Offset Low Register (ESMIOFFLR)

Figure 16-22. ESM Interrupt Offset Low Register (ESMIOFFLR) [offset = 2Ch]

31 16

Reserved

R-0

15 8 7 0

Reserved INTOFFL

R-0 R-0

LEGEND: R = Read only; -n = value after reset

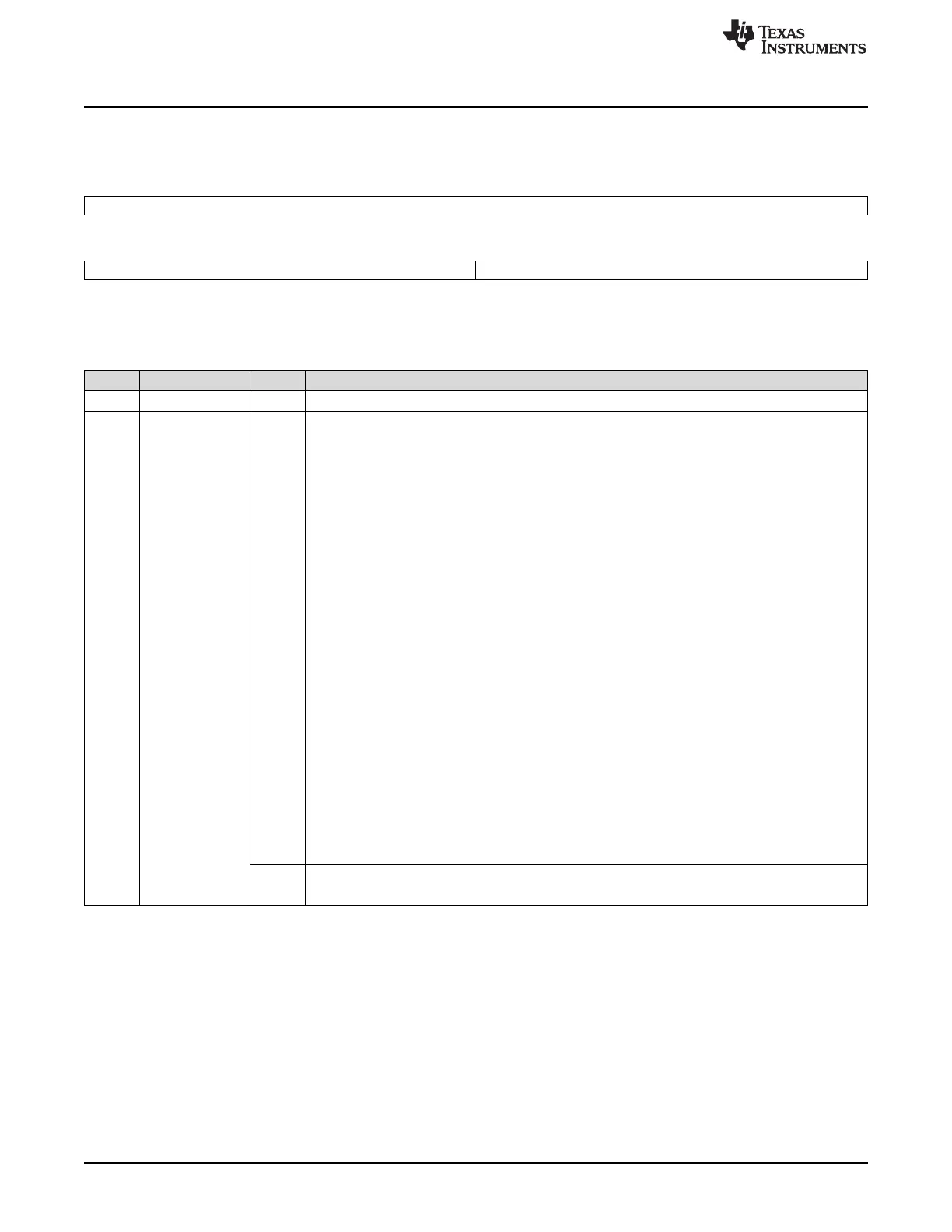

Table 16-14. ESM Interrupt Offset Low Register (ESMIOFFLR) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reads return 0. Writes have no effect.

7-0 INTOFFL Offset Low-Level Interrupt. This vector gives the channel number of the highest-pending interrupt

request for the low-level interrupt line. Inside a group, channel 0 has highest priority and channel 31

has lowest priority.

User and privileged mode (read):

Returns number of pending interrupt with the highest priority for the low-level interrupt line.

0 No pending interrupt.

1h Interrupt pending for channel 0, error Group1.

: :

20h Interrupt pending for channel 31, error Group1.

21h Reserved

: :

40h Reserved

41h Interrupt pending for channel 32, error Group1.

: :

60h Interrupt pending for channel 63, error Group1.

61h Reserved

: :

80h Reserved

81h Interrupt pending for channel 64, error Group1.

: :

A0h Interrupt pending for channel 95, error Group1.

Note: Reading the interrupt vector will not clear the corresponding flag in the ESMSR1 register.

Group2 interrupts are fixed to the high level interrupt line only.

User and privileged mode (write):

Writes have no effect.

Loading...

Loading...