Flash Control Registers

www.ti.com

368

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

F021 Level 2 Flash Module Controller (L2FMC)

7.10.16 Flash Pump Access Control Register 1 (FPAC1)

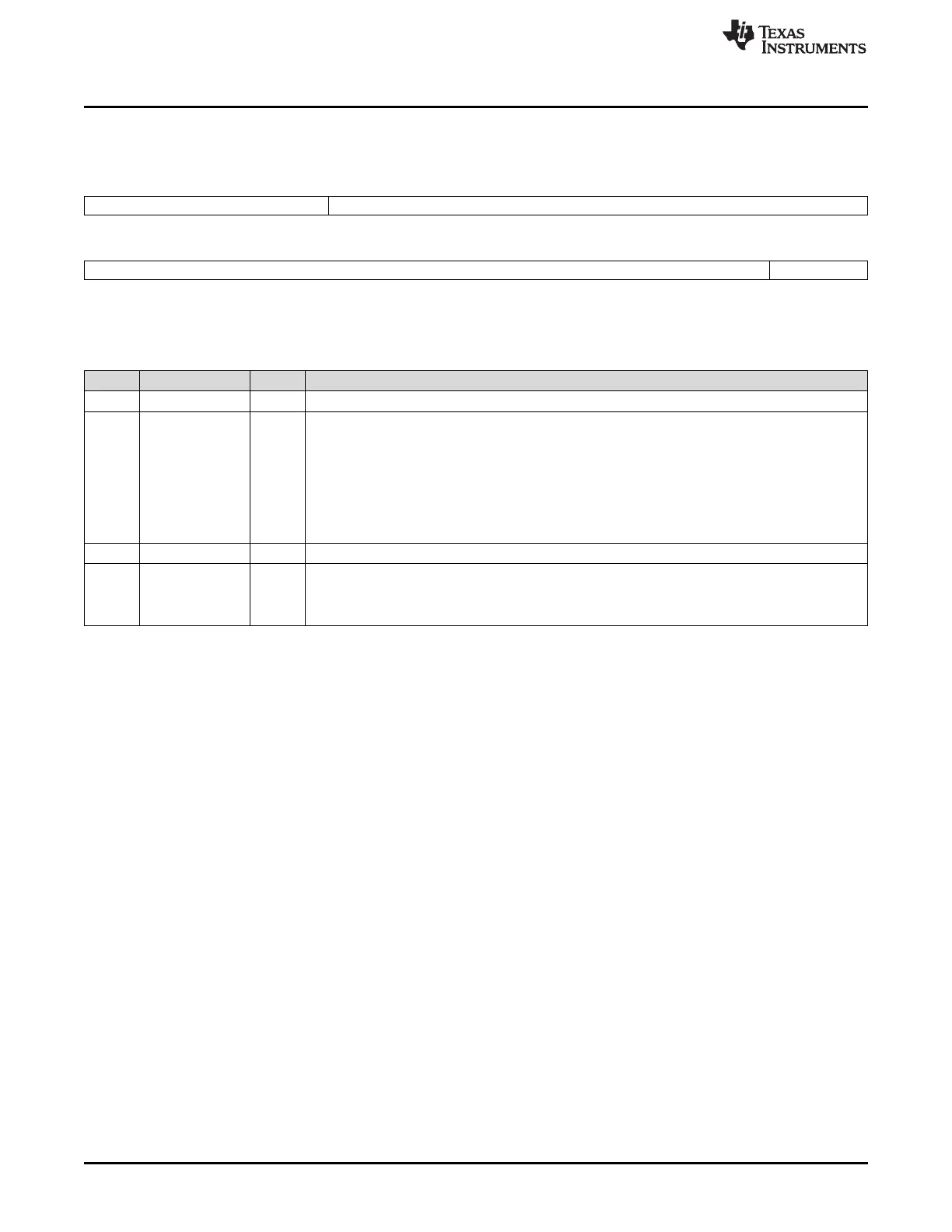

Figure 7-26. Flash Pump Access Control Register 1 (FPAC1) (offset = 48h)

31 27 26 16

Reserved PSLEEP

R-0 R/WP-C8h

15 1 0

Reserved PUMPPWR

R-0 R/WP-1

LEGEND: R/W = Read/Write; R = Read only; WP = Write in Privilege Mode; -n = value after reset

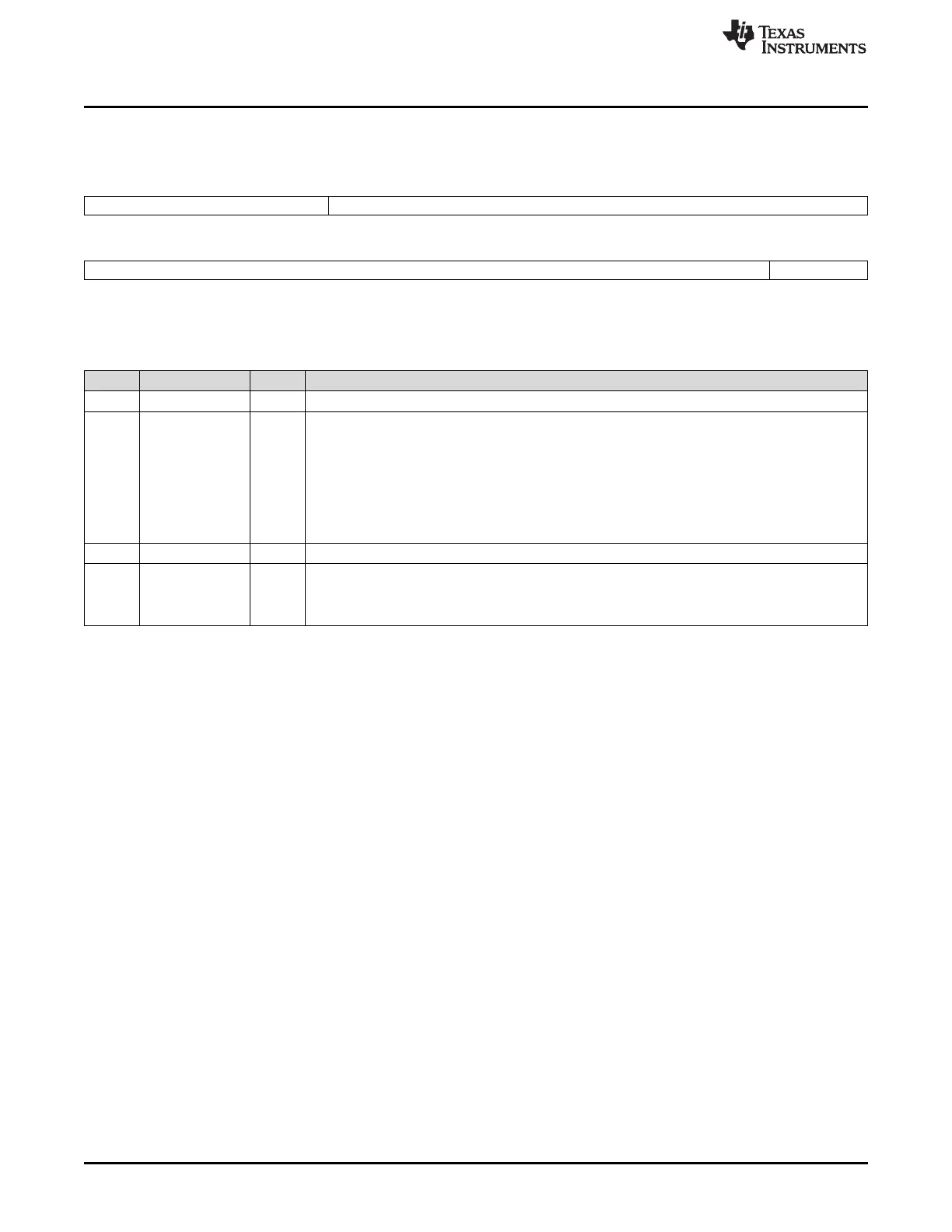

Table 7-28. Flash Pump Access Control Register 1 (FPAC1) Field Descriptions

Bit Field Value Description

31-12 Reserved 0 Reads return 0. Writes have no effect.

26-16 PSLEEP 0-7FFh Pump Sleep.

These bits contain the starting count value for the charge pump sleep down counter. While the

charge pump is in sleep mode, the power mode management logic holds the charge pump sleep

counter at this value. When the charge pump exits sleep power mode, the down counter delays

from 0 to PSLEEP pump sleep down clock cycles before putting the charge pump into active power

mode.

Note: Pump sleep down counter clock is a divide by 2 input of HCLK. That is, there are 2 × HCLK

cycles for every PSLEEP counter cycle.

15-1 Reserved 0 Reads return 0. Writes have no effect.

0 PUMPPWR Flash Charge Pump Fallback Power Mode

0 Sleep (all pump circuits are disabled)

1 Active (all pump circuits are active)

Loading...

Loading...