DCAN Control Registers

www.ti.com

1468

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

27.17.12 ECC Single-Bit Error Code Register (DCAN ECC SERR)

If an ECC single-bit error is detected, the SEFLG flag is set in the ECC Control and Status Register. In

addition to the SEFLG flag, the ECC Single-Bit Error Code Register indicates the memory area where the

single-bit error has been detected (message object number only).

If more than one word with an ECC single-bit error is detected, the highest word number with an ECC

single-bit error is displayed.

After an ECC single-bit error is detected, the register holds the last error code until power is removed.

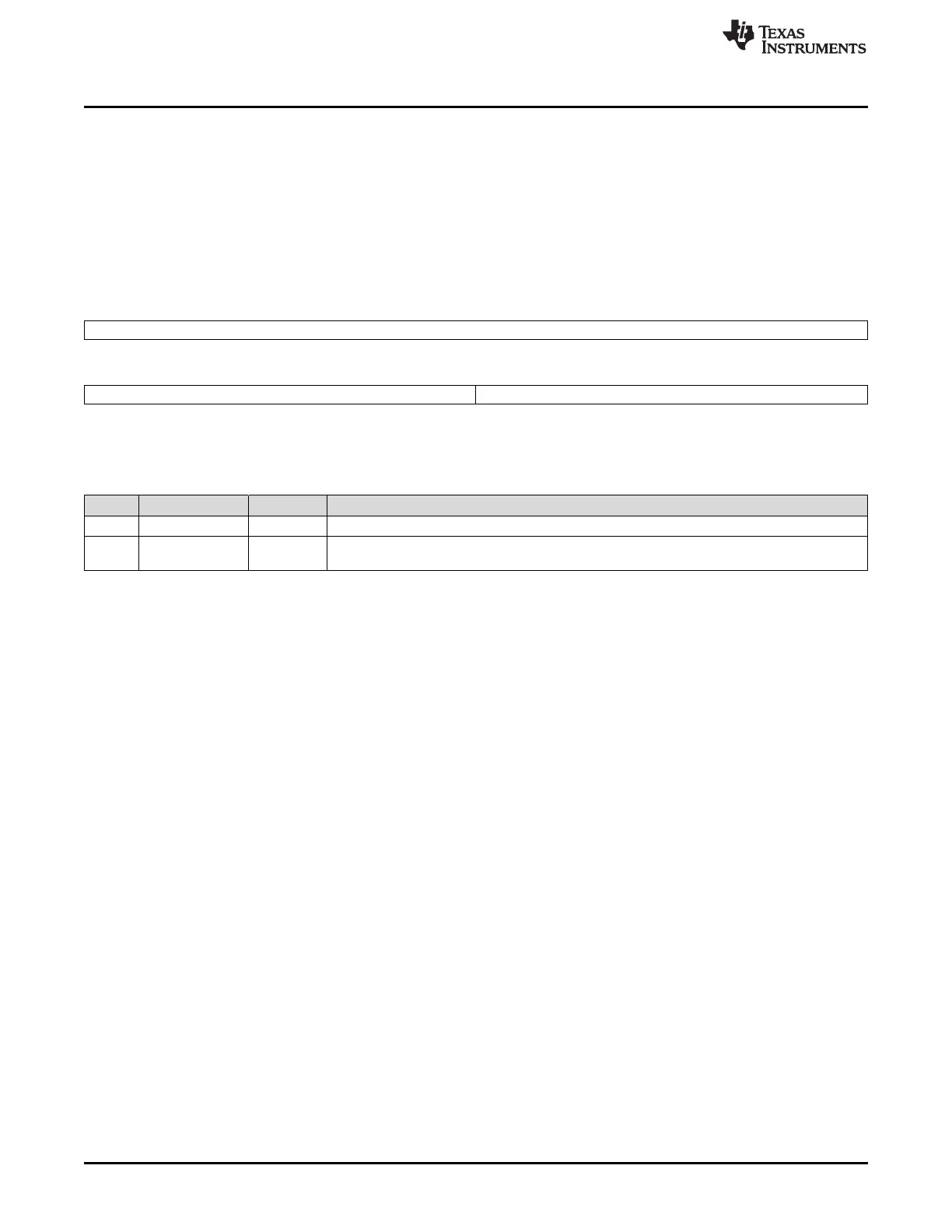

Figure 27-31. ECC Single-Bit Error Code Register (DCAN ECC SERR) [offset = 30h]

31 16

Reserved

R-0

15 8 7 0

Reserved Message Number

R-0 R-U

LEGEND: R = Read only; -n = value after reset; U = value is undefined

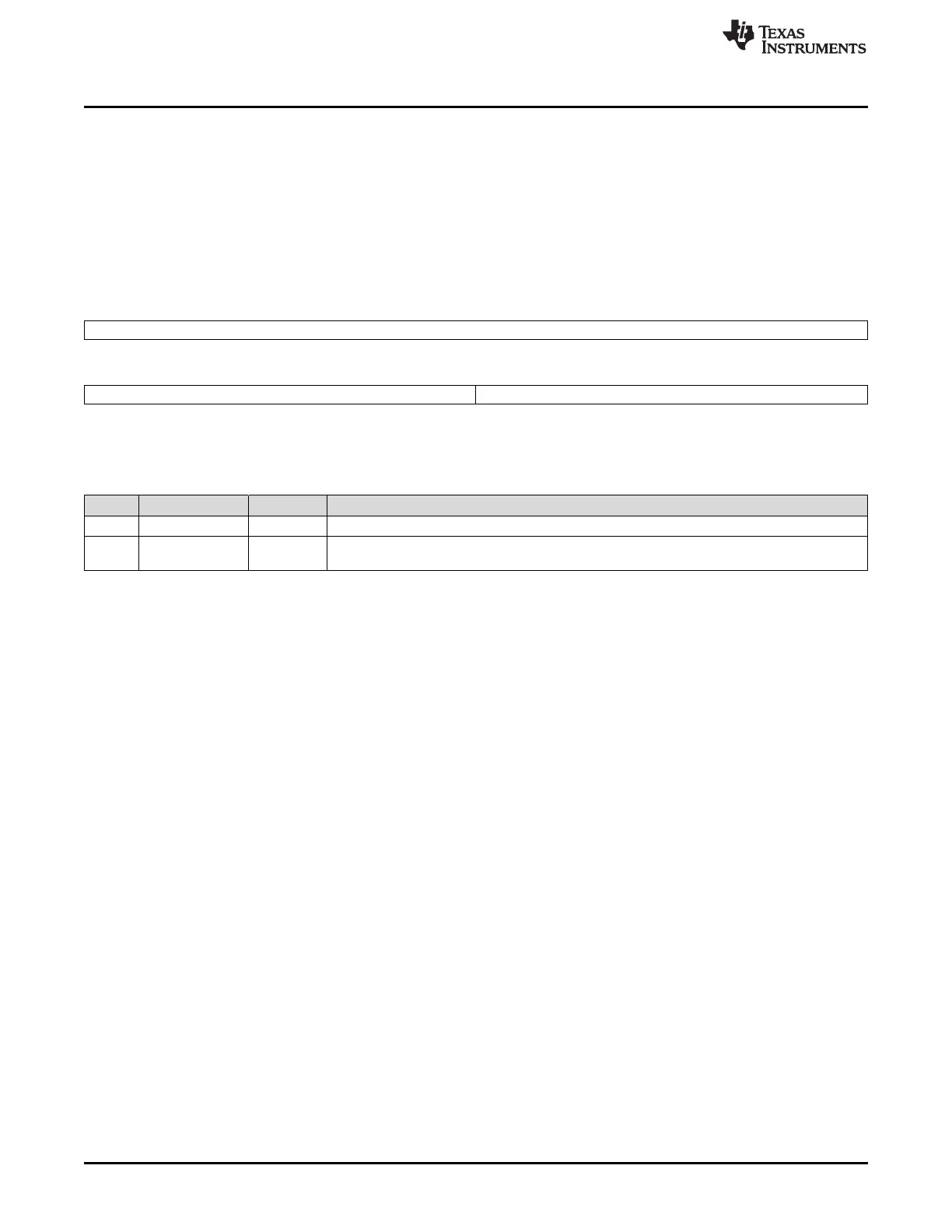

Table 27-18. ECC Single-Bit Error Code Register (DCAN ECC SERR) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 These bits are always read as 0. Writes have no effect.

7-0 Message Number 1h-FFh Message object number where ECC single-bit error has been detected. Only values 1h-40h are

valid. Values 41h-FFh are invalid.

Loading...

Loading...