www.ti.com

DCAN Control Registers

1467

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

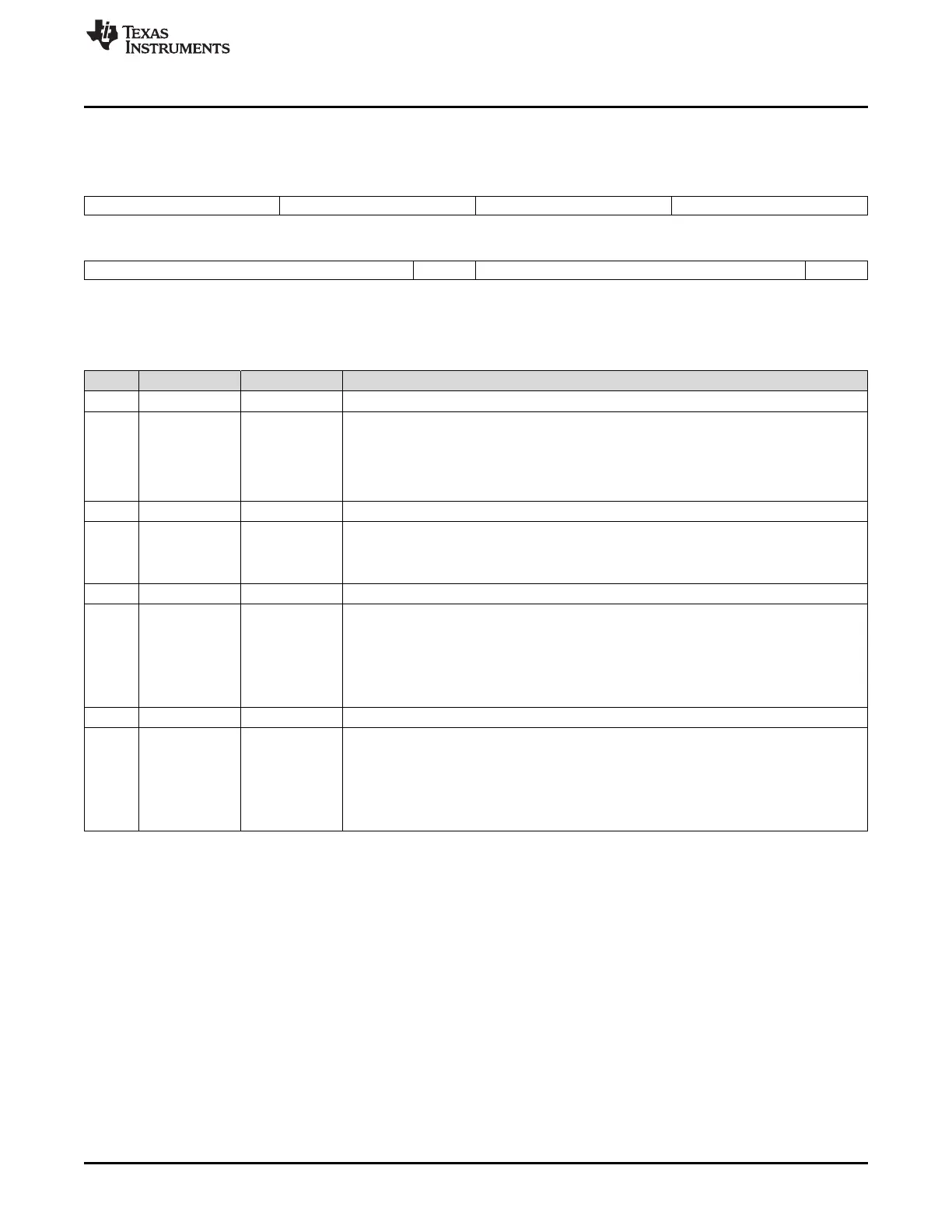

27.17.11 ECC Control and Status Register (DCAN ECC CS)

Figure 27-30. ECC Control and Status Register (DCAN ECC CS) [offset = 2Ch]

31 28 27 24 23 20 19 16

Reserved SBE_EVT_EN Reserved ECCMODE

R-0 R/WP-5h R-0 R/WP-Ah

15 9 8 7 1 0

Reserved DEFLG Reserved SEFLG

R-0 R/W1C-0 R-0 R/W1C-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear; WP = Write in privileged mode only; -n = value after reset

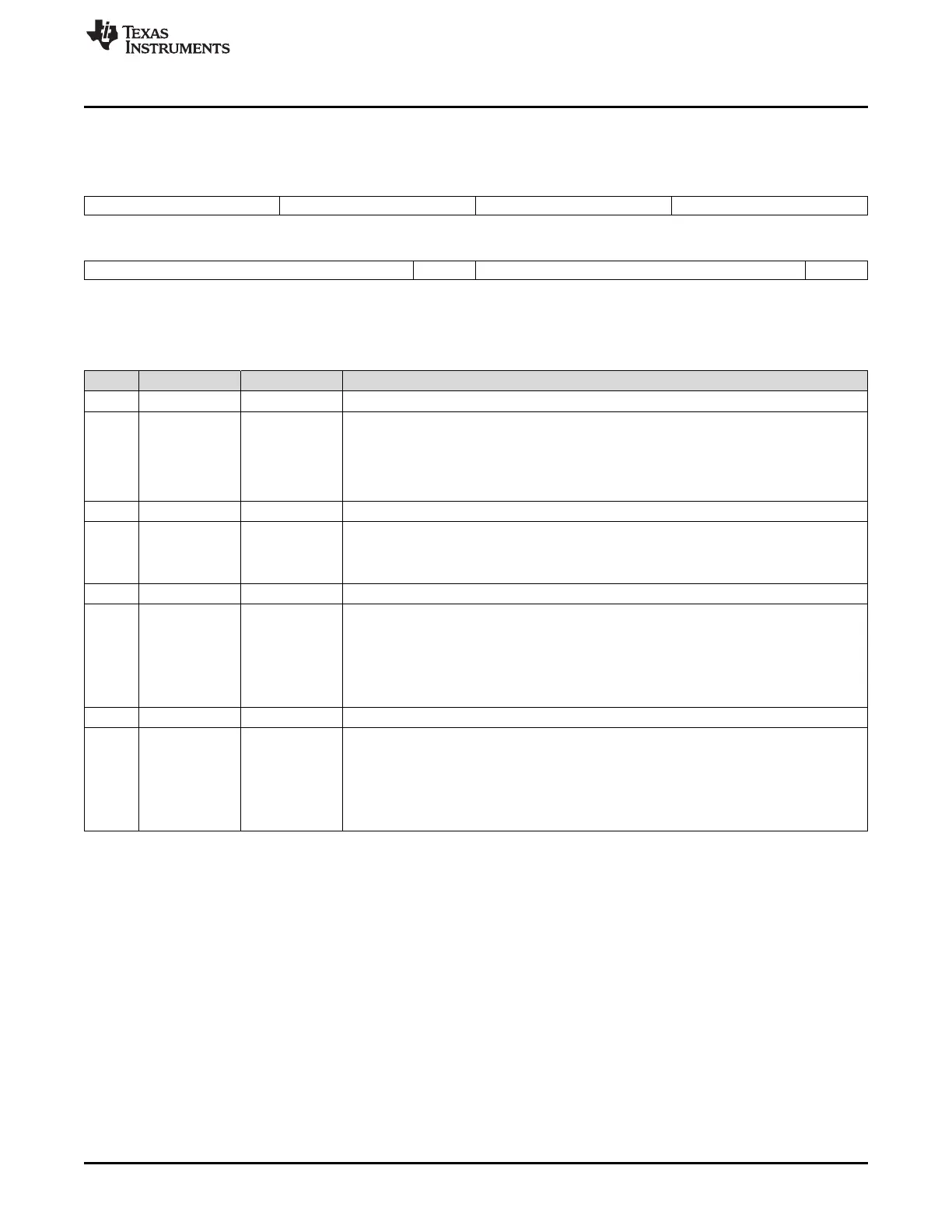

Table 27-17. ECC Control and Status Register (DCAN ECC CS) Field Descriptions

Bit Field Value Description

31-9 Reserved 0 These bits are always read as 0. Writes have no effect.

27-24 SBE_EVT_EN Enable SECDED single-bit error event (CAN_SERR signal).

5h SECDED single-bit error event is disabled, single-bit errors are not signaled with a high pulse

on DCAN_SERR signal.

All other values SECDED single-bit error event is enabled, single-bit errors are signaled with a high pulse on

DCAN_SERR signal.

23-20 Reserved 0 These bits are always read as 0. Writes have no effect.

19-16 ECCMODE Enable SECDED single-bit error correction.

5h SECDED single-bit error correction is disabled.

All other values SECDED single-bit error correction is enabled.

15-9 Reserved 0 These bits are always read as 0. Writes have no effect.

8 DEFLG Double-bit error flag.

0

Read: No double-bit error is detected.

Write: The bit is unchanged.

1

Read: Double-bit error is detected.

Write: The bit is cleared to 0.

7-1 Reserved 0 These bits are always read as 0. Writes have no effect.

0 SEFLG Single-bit error flag.

0

Read: No single-bit error is detected.

Write: The bit is unchanged.

1

Read: Single-bit error is detected.

Write: The bit is cleared to 0.

Loading...

Loading...