Control and Status Registers

www.ti.com

396

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Level 2 RAM (L2RAMW) Module

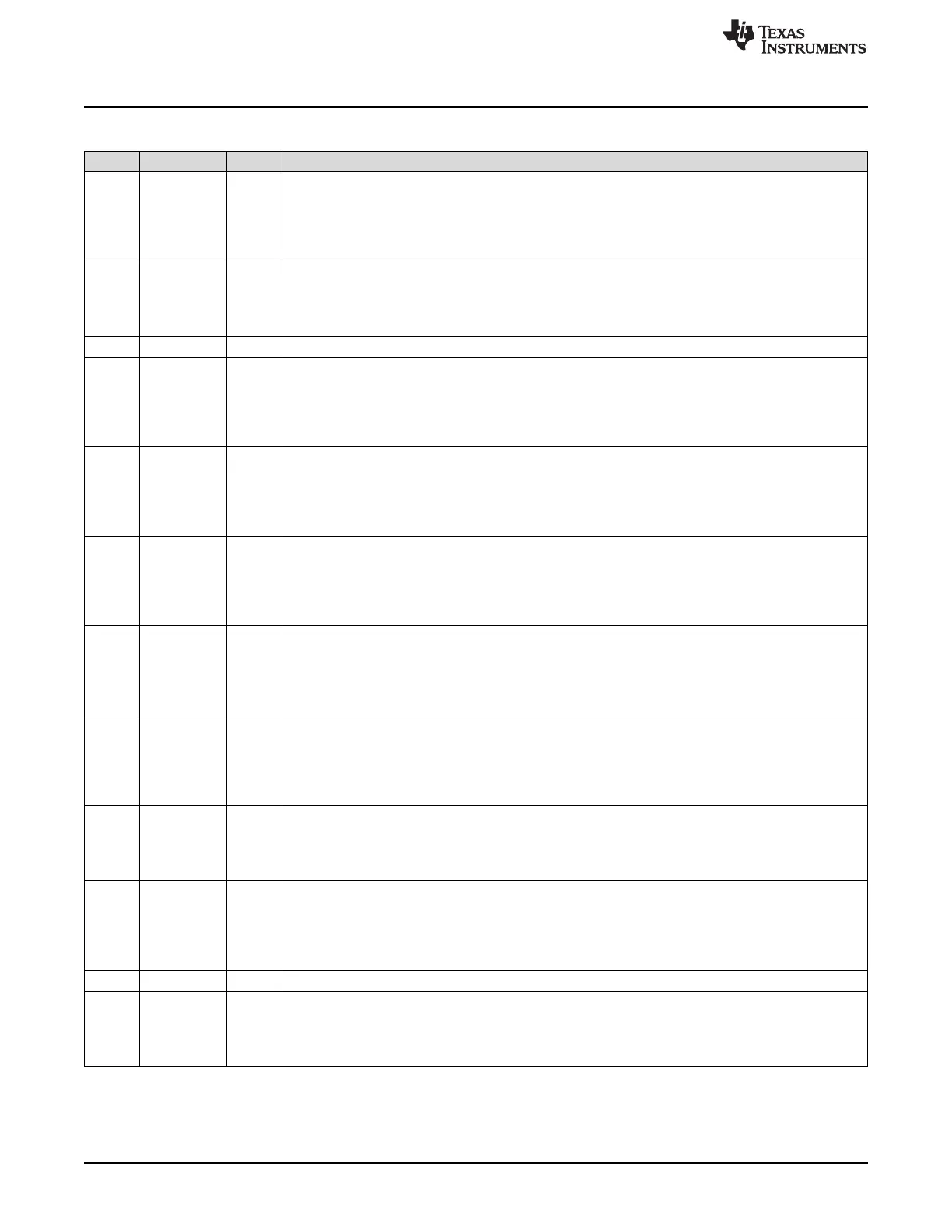

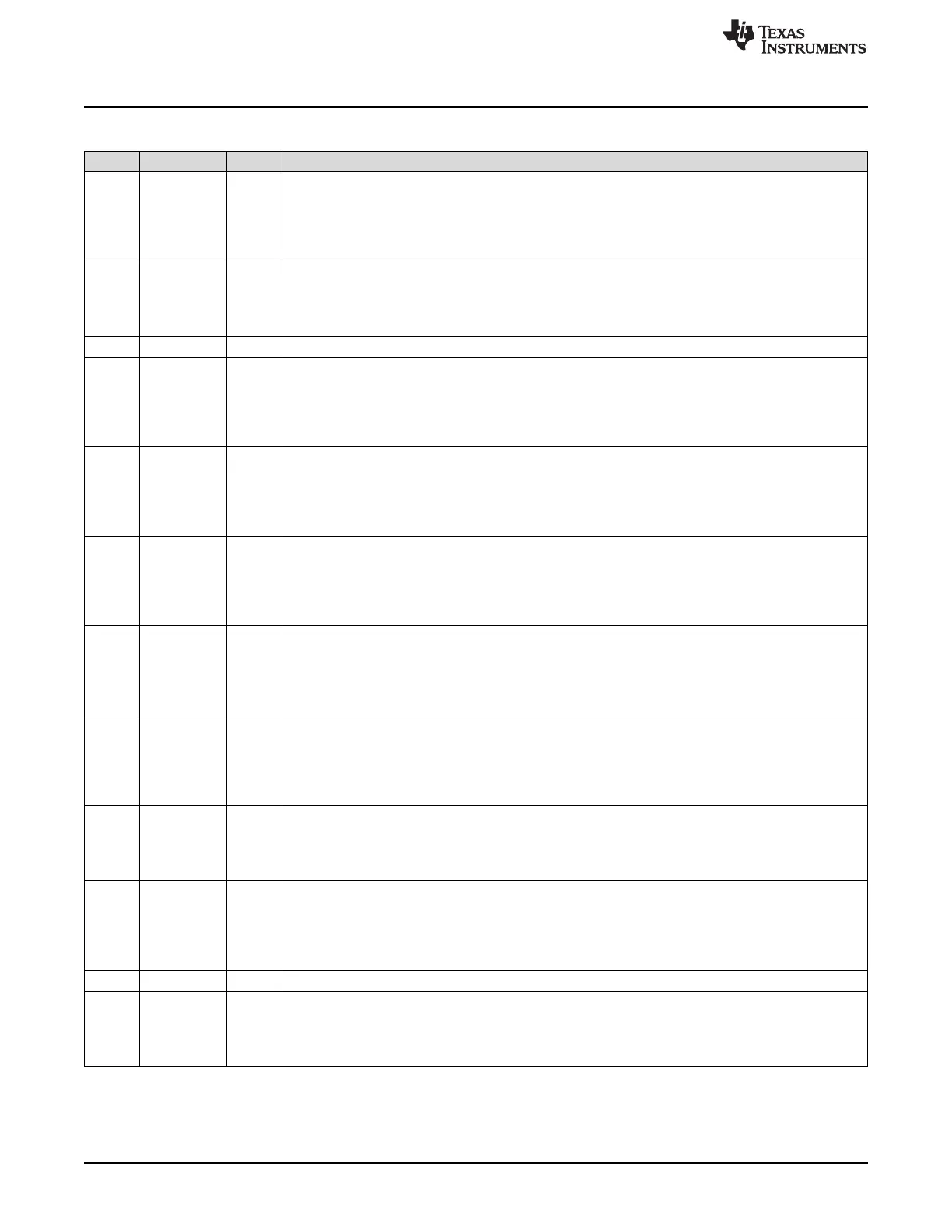

Table 8-4. L2RAMW Module Error Status Register (RAMERRSTATUS) Field Descriptions (continued)

Bit Field Value Description

16 MSACP Memory Scrubbing write back Redundant Address decode error. This bit indicates that an address-

control parity error occurred during memory scrubbing write back. This bit must be cleared by writing a 1

to it before any new error can be generated.

0 An address control parity error did not occur during memory scrubbing write back.

1 An address control parity error occurred during memory scrubbing write back.

15 CPEOI Command Parity Error on Idle. This bit indicates an error occurred for an idle command with parity error.

This bit must be cleared by writing a 1 to it before any new error can be generated.

0 An error did not occur.

1 An error occurred.

14 Reserved 0 Reads return 0. Writes have no effect.

13 MIE Memory Initialization Error. This bit indicated an error occurred for an access to a bank under memory

initialization. Access to a bank under memory initialization is not allowed. It will result in a false double

bit error. This bit must be cleared by writing a 1 to it before any new error can be generated.

0 An error did not occur.

1 An error occurred.

12 MMDE Merged MUX Diagnostic Error. This bit indicates a error was detected on the compare logic of the mux

logic used for data merging of a read modify write operation during diagnostic test. This bit must be

cleared by writing a 1 to it before any new error can be generated.

0 An error did not occur.

1 An error occurred.

11 WEMDE Write ECC Malfunction Diagnostic Error. This bit indicated an error was detected on the compare logic

of the write ECC malfunction during diagnostic test. This bit must be cleared by writing a 1 to it before

any new error can be generated.

0 An error did not occur.

1 An error occurred.

10 REMDE Read ECC Malfunction Diagnostic Error. This bit indicated an error was detected on the compare logic

of the read ECC malfunction during diagnostic test. This bit must be cleared by writing a 1 to it before

any new error can be generated.

0 An error did not occur.

1 An error occurred.

9 MME Merged Mux Error. This bit indicates an error was detected on the mux logic that is used to merge the

corrected read and write data for a read modify write operation. This bit must be cleared by writing a 1

to it before any new error can be generated.

0 An error did not occur.

1 An error occurred.

8 PACE Address and/or Control bus Parity Error. This bit must cleared by writing a 1 to it before any new error

can be generated.

0 An error did not occur.

1 An error occurred.

7 RMWDE Read-Modify-Write Double Bit Error. This bit indicates that an ECC uncorrectable (double bit) error was

detected during read access of the read modify write operation. This bit must be cleared by writing a 1

to it before any new error can be generated.

0 An error did not occur.

1 An error occurred.

6 Reserved 0 Reads return 0. Writes have no effect.

5 CPUWDE CPU Write Double-bit Error. This bit indicates that an ECC uncorrectable (double bit) error was detected

during write access. This bit must be cleared by writing a 1 to it before any new error can be generated.

0 An error did not occur.

1 An error occurred.

Loading...

Loading...