www.ti.com

Control and Status Registers

397

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Level 2 RAM (L2RAMW) Module

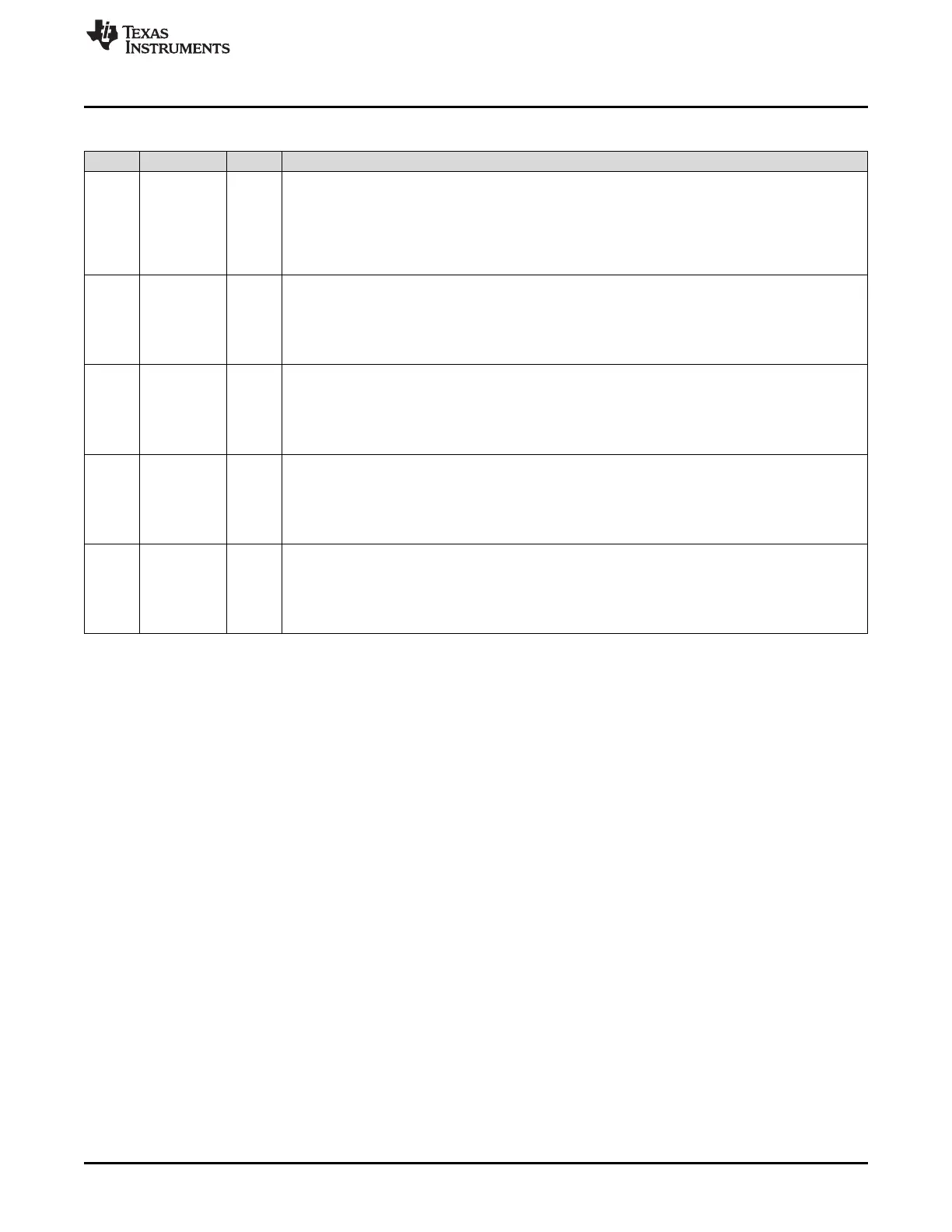

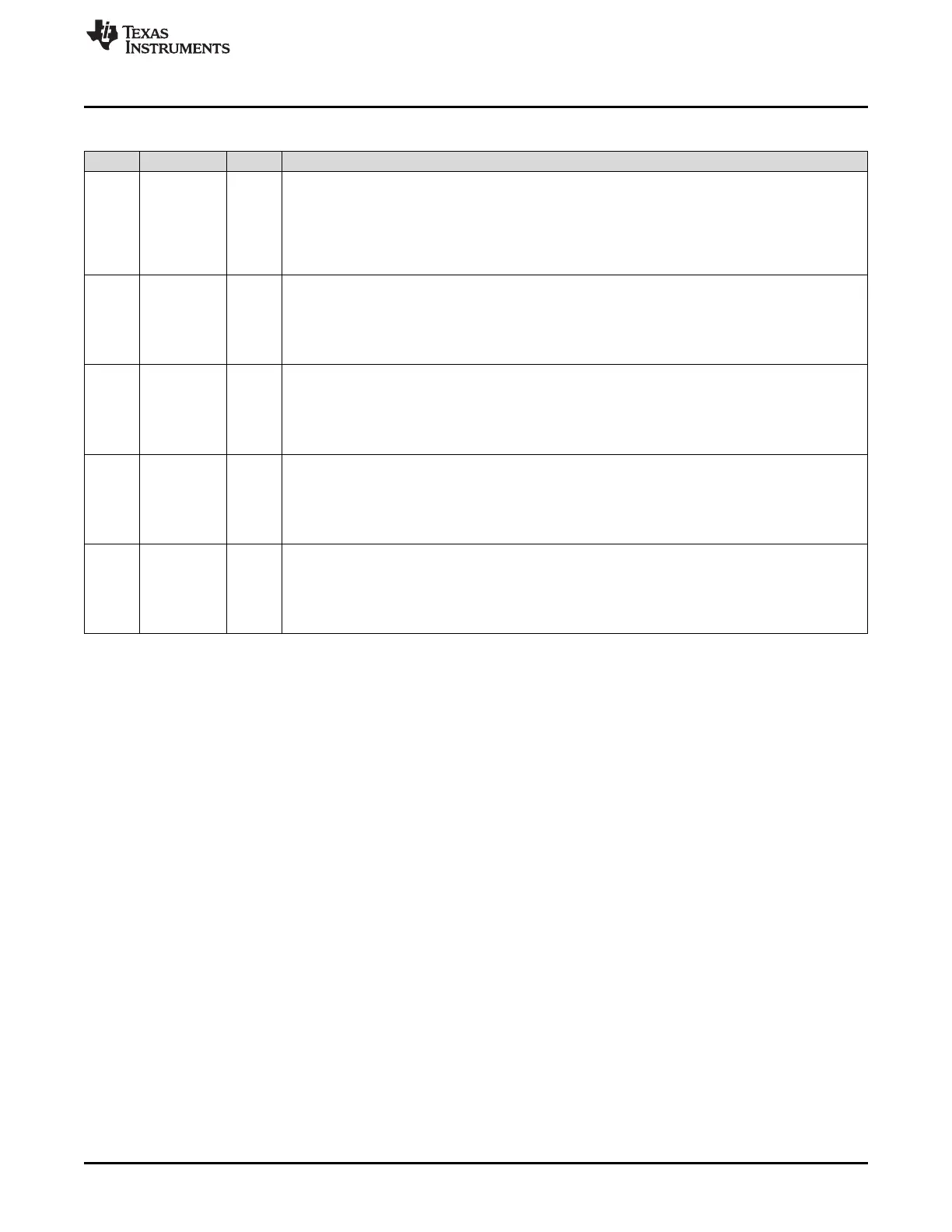

Table 8-4. L2RAMW Module Error Status Register (RAMERRSTATUS) Field Descriptions (continued)

Bit Field Value Description

4 ADDE Redundant address decoding diagnostic error. This bit indicates that the redundant address decode

logic diagnostic test has detected that a compare element has malfunctioned during the testing of the

logic. This bit is only set in test mode. This bit must be cleared by writing a 1 to it for generation of any

new uncorrectable error interrupt in non-test mode.

0 An error did not occur.

1 An error occurred.

3 WEME Write ECC Malfunction Error. This bit Indicates that the SECDED logic failed to correct a single bit error

during a CPU write operation. This bit must be cleared by writing a 1 to it before any new error can be

generated.

0 An error did not occur.

1 An error occurred.

2 ADE Address Decode Error. This bit indicates than an address error was generated by the redundant

address decode logic due to a functional failure. This bit must be cleared by writing a 1 to it before any

new error can be generated.

0 An error did not occur.

1 An error occurred.

1 REME Read ECC Malfunction Error. Indicates that the SECDED logic failed to correct a single bit error on the

read of a read-modify-write operation. This bit must be cleared by writing a 1 to it before any new error

can be generated.

0 An error did not occur.

1 An error occurred.

0 CPUWE CPU Write Single Error. This bit indicates that a single-bit error occurred during write access. This bit

must be cleared by writing 1 to it in order to clear the interrupt request and to enable subsequent single-

bit error interrupt generation.

0 An error did not occur.

1 An error occurred.

Loading...

Loading...