Multi-buffer RAM

www.ti.com

1610

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

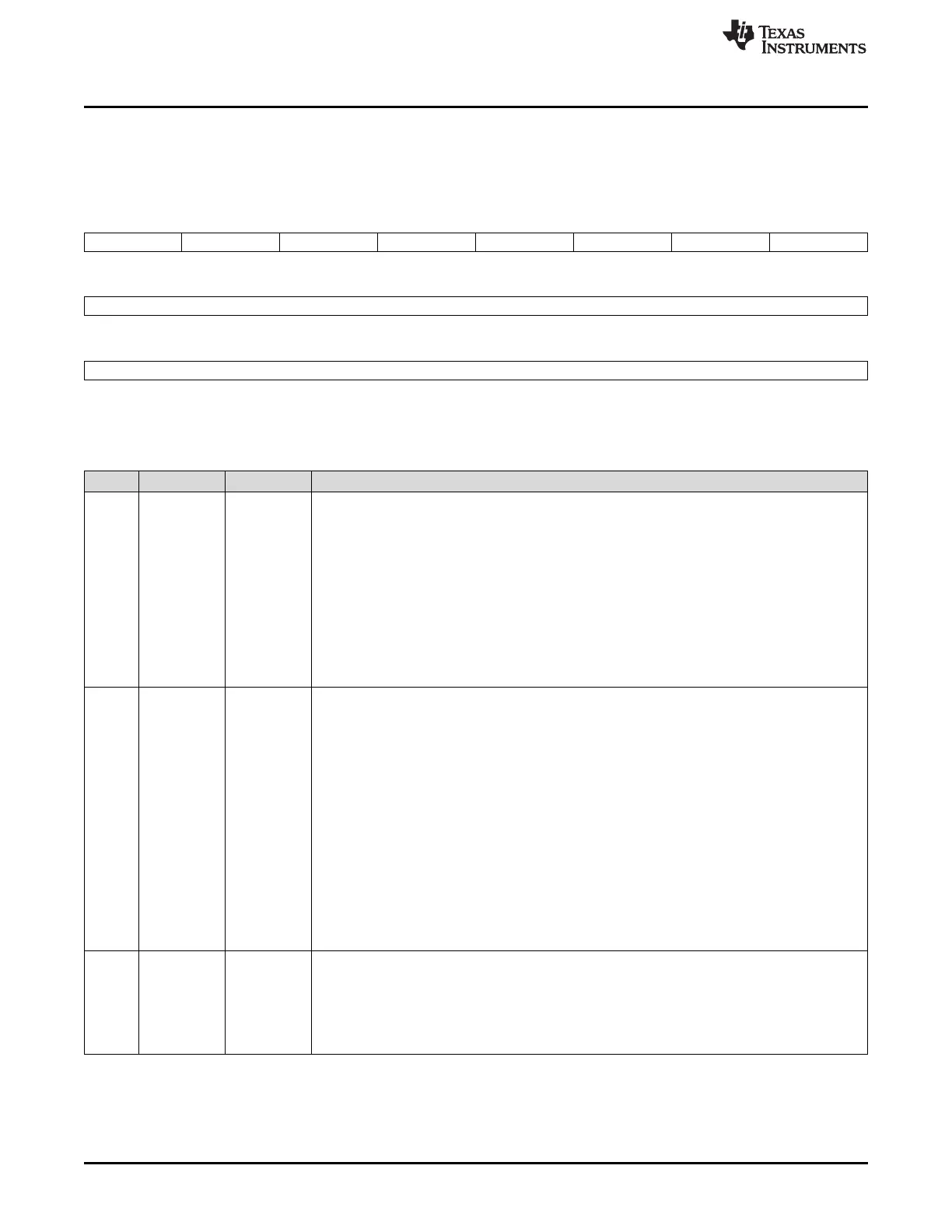

28.4.4 Multi-buffer RAM Receive Buffer Register (RXRAM)

Each word of RXRAM is a receive-buffer register.

Figure 28-89. Multi-buffer RAM Receive Buffer Register (RXRAM)

[offset = RAM Base + 200-3FFh]

31 30 29 28 27 26 25 24

RXEMPTY RXOVR TXFULL BITERR DESYNC PARITYERR TIMEOUT DLENERR

RS-1 RC-0 R-0 RC-0 RC-0 RC-0 RC-0 RC-0

23 16

LCSNR

R-0

15 0

RXDATA

R/W-0

LEGEND: R = Read only; R/W = Read/Write; C = Clear; S = Set; -n = value after reset

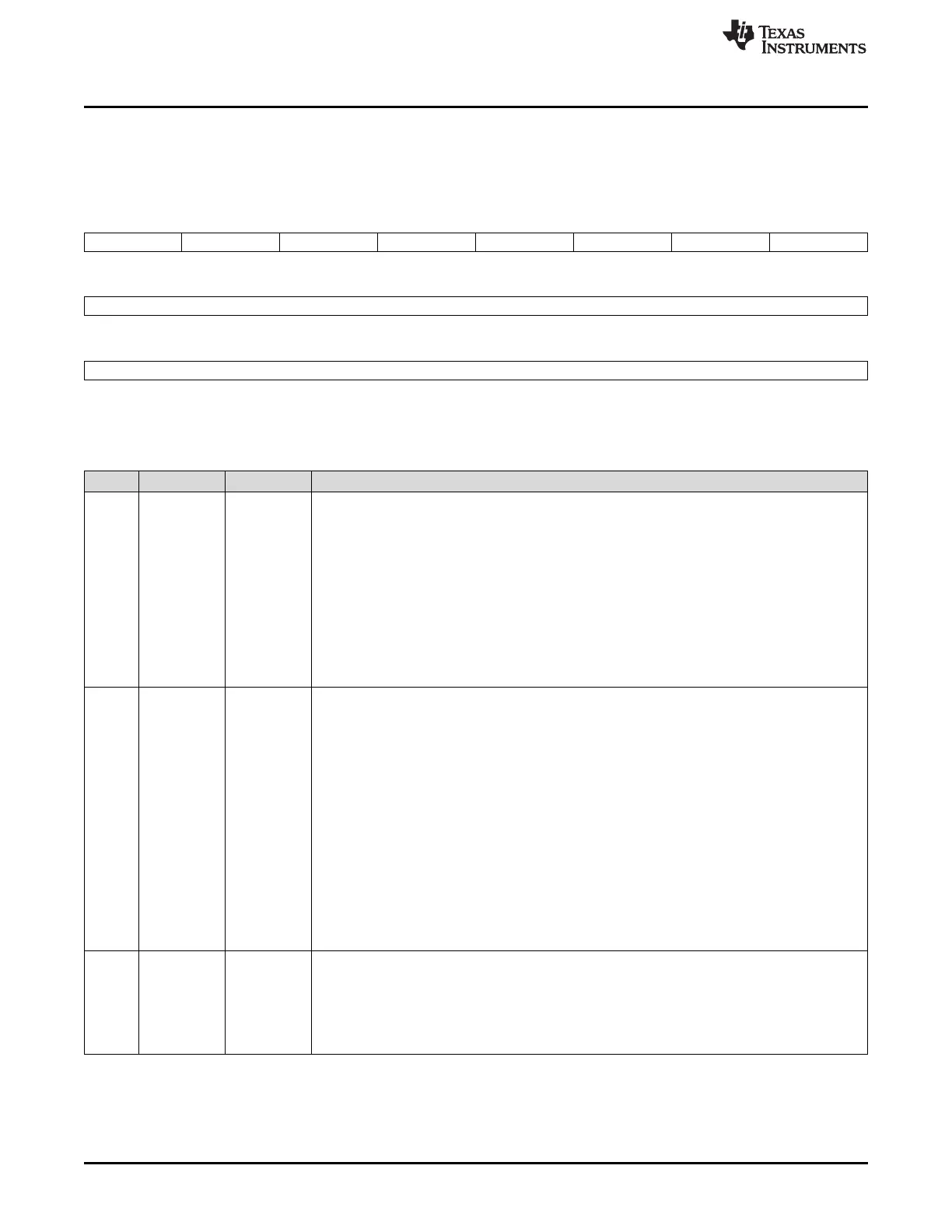

Table 28-64. Multi-buffer Receive Buffer Register (RXRAM) Field Descriptions

Bit Field Value Description

31 RXEMPTY Receive data buffer empty. When the host reads the RXDATA field or the entire RXRAM register,

it automatically sets the RXEMPTY flag. When a data transfer is completed, the received data is

copied into RXDATA, and the RXEMPTY flag is cleared.

0 New data has been received and copied into RXDATA.

1 No data has been received since the last read of RXDATA.

This flag gets set to 1 under the following conditions:

• Reading the RXDATA field of the RXRAM register.

• Writing a 1 to clear the RXINTFLG bit in the SPI Flag Register (SPIFLG).

Write-clearing the RXINTFLG bit before reading RXDATA indicates the received data is being

ignored. Conversely, RXINTFLG can be cleared by reading the RXDATA field of RXRAM (or the

entire register).

30 RXOVR Receive data buffer overrun. When a data transfer is completed and the received data is copied

into RXBUF while it is already full, RXOVR is set. Overruns always occur to RXBUF, not to

RXRAM; the contents of RXRAM are overwritten only after it is read by the Peripheral (VBUSP)

master (CPU, DMA, or other host processor).

If enabled, the RXOVRN interrupt is generated when RXBUF is overwritten, and reading either SPI

Flag Register (SPIFLG) or SPIVECTx shows the RXOVRN condition. Two read operations from

the RXRAM register are required to reach the overwritten buffer word (one to read RXRAM, which

then transfers RXDATA into RXRAM for the second read).

Note: This flag is cleared to 0 when the RXDATA field of the RXRAM register is read.

Note: A special condition under which RXOVR flag gets set.If both RXRAM and RXBUF are

already full and while another buffer receive is underway, if any errors such as TIMEOUT,

BITERR and DLEN_ERR occur, then RXOVR in RXBUF and SPI Flag Register (SPIFLG) will

be set to indicate that the status flags are getting overwritten by the new transfer. This

overrun should be treated like a normal receive overrun.

0 No receive data overrun condition occurred since last read of the data field.

1 A receive data overrun condition occurred since last read of the data field.

29 TXFULL Transmit data buffer full. This flag is a read-only flag. Writing into the SPIDAT0 or SPIDAT1 field

while the TX shift register is full will automatically set the TXFULL flag. Once the word is copied to

the shift register, the TXFULL flag will be cleared. Writing to SPIDAT0 or SPIDAT1 when both

TXBUF and the TX shift register are empty does not set the TXFULL flag.

0 The transmit buffer is empty; SPIDAT0/SPIDAT1 is ready to accept a new data.

1 The transmit buffer is full; SPIDAT0/SPIDAT1 is not ready to accept new data.

Loading...

Loading...