TC1796

System Units (Vol. 1 of 2)

Register Overview

User’s Manual 18-105 V2.0, 2007-07

Regs, V2.0

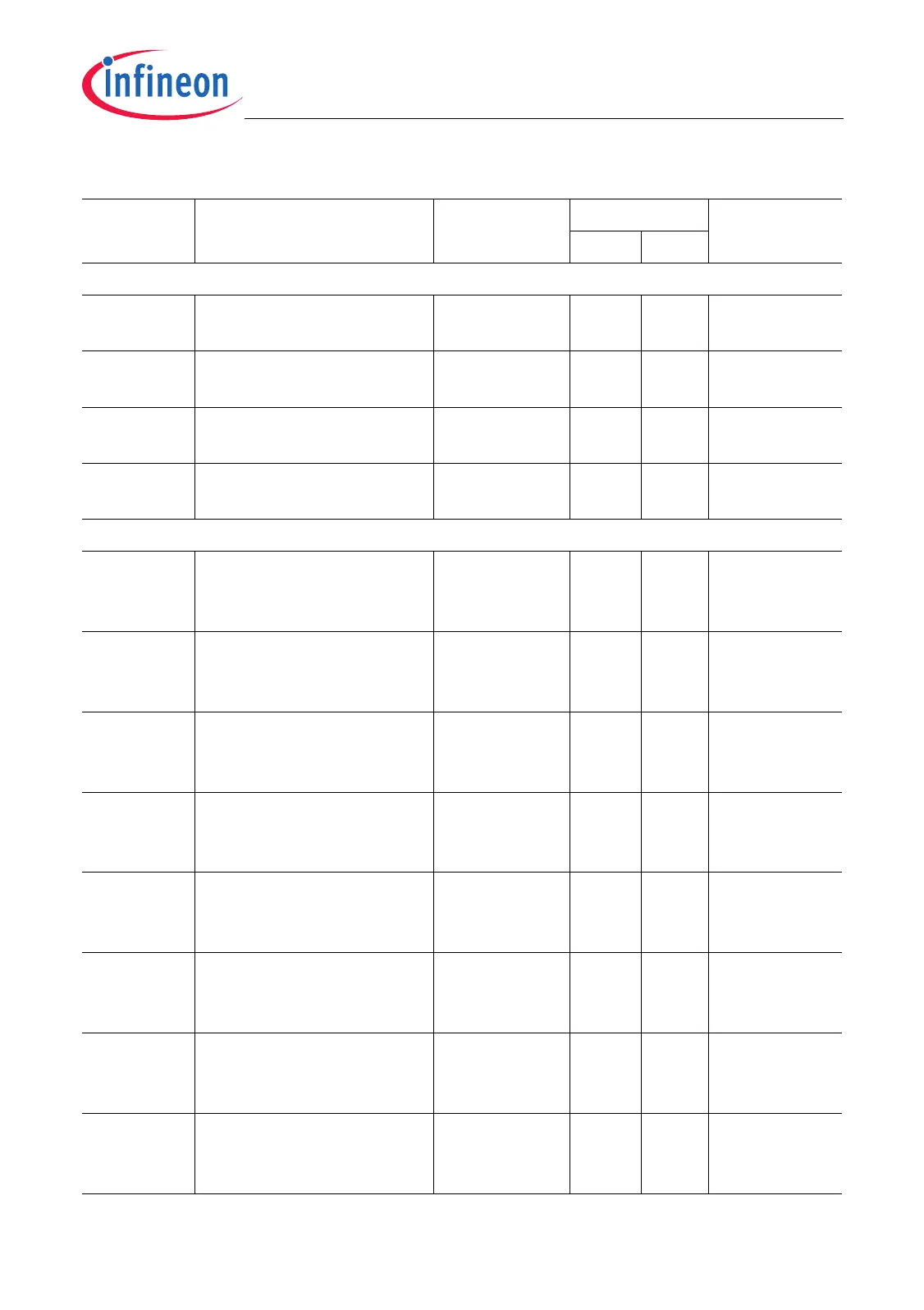

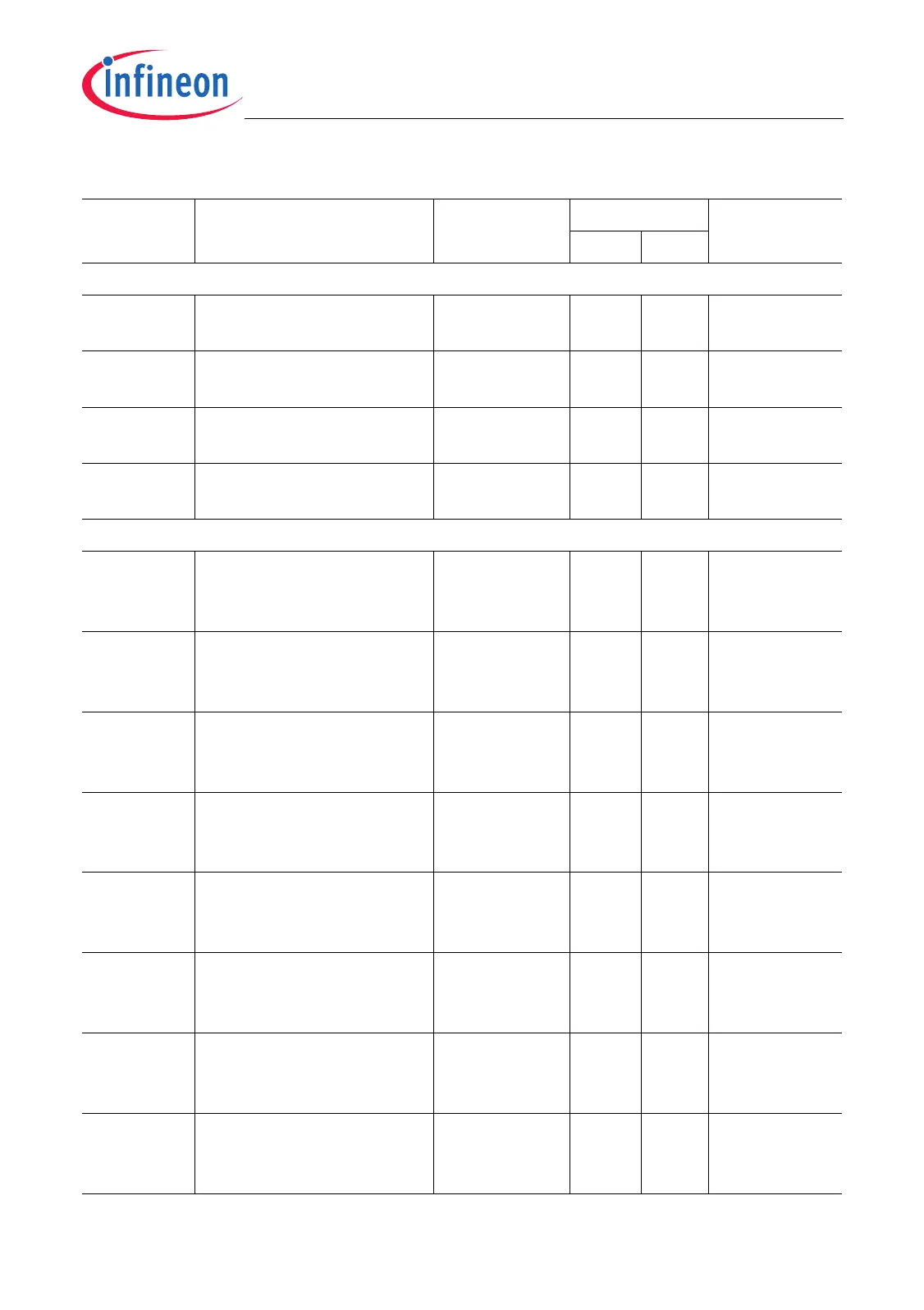

Table 18-33 Address Map of CPU Core SFRs & GPRs

Short

Name

Description Address Access Mode Reset Value

Read Write

CPU Core SFRs & GPRs

– Reserved F7E1 0000

H

-

F7E1 7FFC

H

BE BE –

MMU_CON MMU Control Register F7E1 8000

H

U, SV,

32

SV,

32

0000 8000

H

– Reserved F7E1 8004

H

-

F7E1 803C

H

U, SV,

32

SV,

32

1)

–

– Reserved F7E1 8400

H

-

F7E1 BFFC

H

BE BE –

Memory Protection Registers

DPR0_0L Data Seg. Prot. Reg. Set

0, Range 0, Lower

Boundary

F7E1 C000

H

U, SV,

32

SV,

32

0000 0000

H

DPR0_0U Data Seg. Prot. Reg. Set

0, Range 0, Upper

Boundary

F7E1 C004

H

U, SV,

32

SV,

32

0000 0000

H

DPR0_1L Data Seg. Prot. Reg. Set

0, Range 1, Lower

Boundary

F7E1 C008

H

U, SV,

32

SV,

32

0000 0000

H

DPR0_1U Data Seg. Prot. Reg. Set

0, Range 1, Upper

Boundary

F7E1 C00C

H

U, SV,

32

SV,

32

0000 0000

H

DPR0_2L Data Seg. Prot. Reg. Set

0, Range 2, Lower

Boundary

F7E1 C010

H

U, SV,

32

SV,

32

0000 0000

H

DPR0_2U Data Seg. Prot. Reg. Set

0, Range 2, Upper

Boundary

F7E1 C014

H

U, SV,

32

SV,

32

0000 0000

H

DPR0_3L Data Seg. Prot. Reg. Set

0, Range 3, Lower

Boundary

F7E1 C018

H

U, SV,

32

SV,

32

0000 0000

H

DPR0_3U Data Seg. Prot. Reg. Set

0, Range 3, Upper

Boundary

F7E1 C01C

H

U, SV,

32

SV,

32

0000 0000

H

Loading...

Loading...