TC1796

Peripheral Units (Vol. 2 of 2)

Synchronous Serial Interface (SSC)

User’s Manual 20-38 V2.0, 2007-07

SSC, V2.1

The Slave Select Output Timing Control Register controls the timing parameters of the

Slave Select Output Generation Unit.

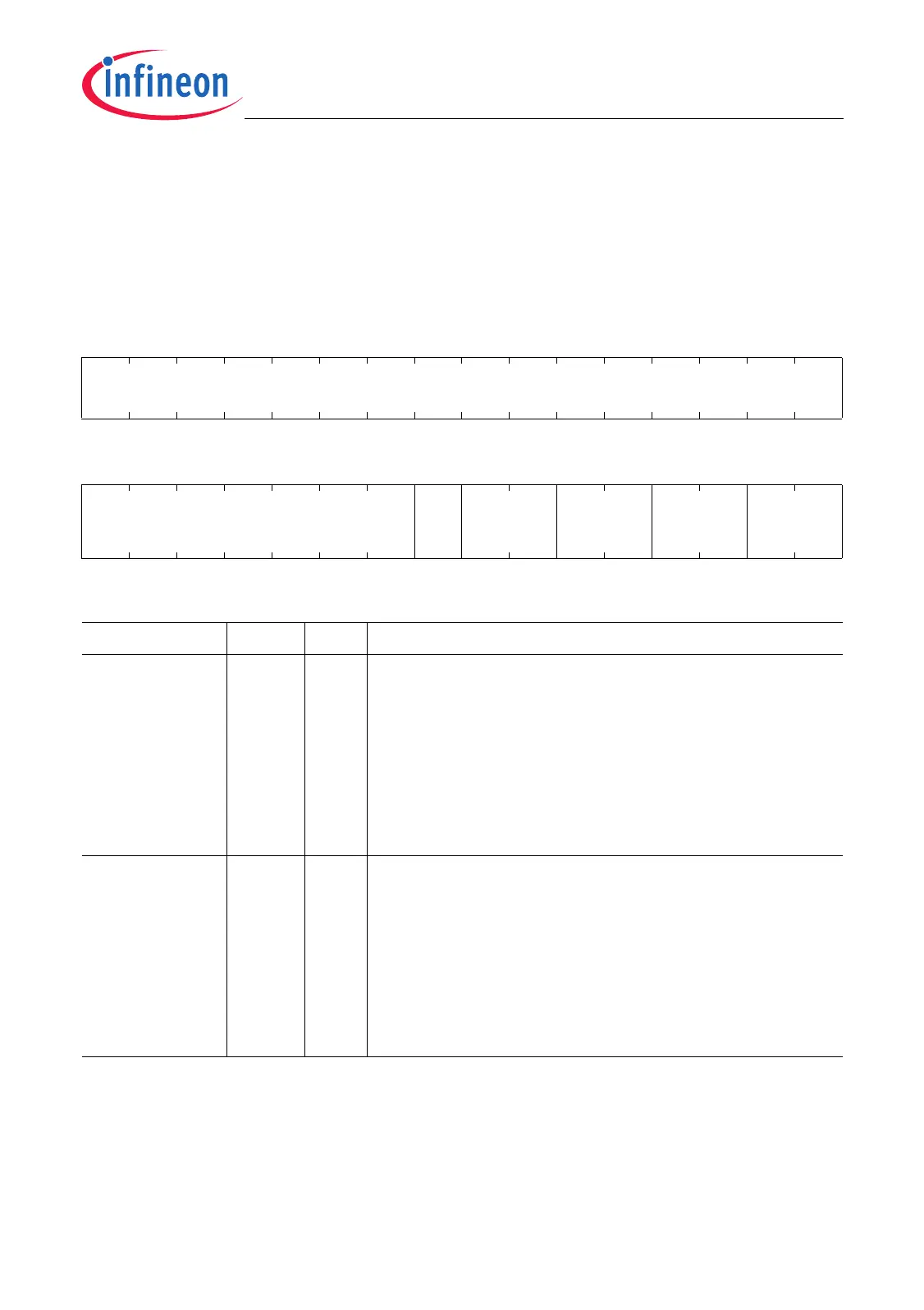

SSOTC

Slave Select Output Timing Control Register

(1C

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0

SLS

O7

MOD

0 INACT TRAIL LEAD

r rw r rw rw rw

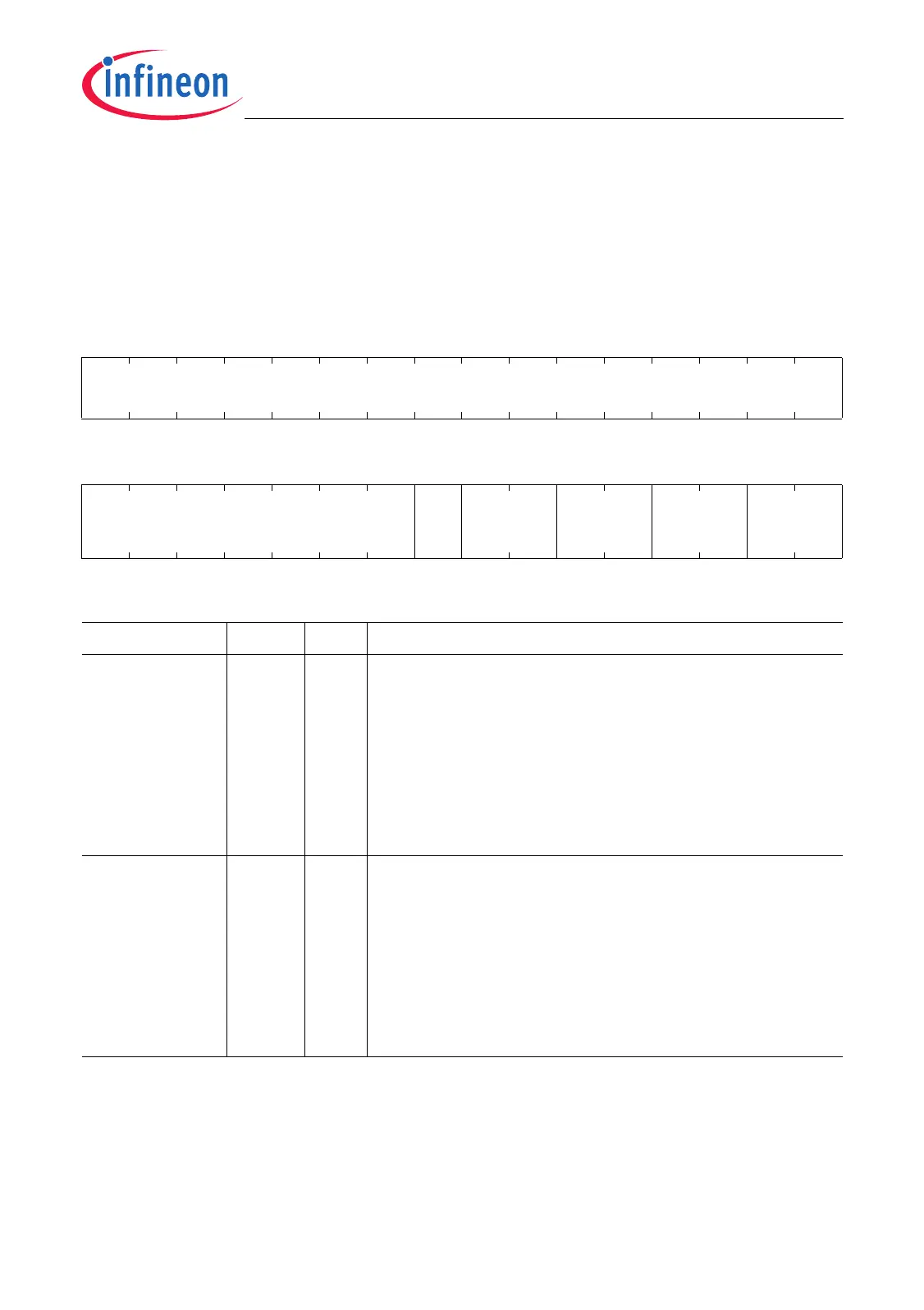

Field Bits Type Description

LEAD [1:0] rw Slave Output Select Leading Delay

This bit field determines the number of leading delay

clock cycles. A leading delay clock cycle is always a

multiple of an SCLK shift clock period.

00

B

Zero leading delay clock cycle selected

1)

01

B

One leading delay clock cycle selected

10

B

Two leading delay clock cycles selected

11

B

Three leading delay clock cycles selected

TRAIL [3:2] rw Slave Output Select Trailing Delay

This bit field determines the number of trailing delay

clock cycles. A trailing delay clock cycle is always a

multiple of an SCLK shift clock period.

00

B

Zero trailing delay clock cycle selected

1)

01

B

One trailing delay clock cycle selected

10

B

Two trailing delay clock cycles selected

11

B

Three trailing delay clock cycles selected

Loading...

Loading...