TC1796

Peripheral Units (Vol. 2 of 2)

Synchronous Serial Interface (SSC)

User’s Manual 20-40 V2.0, 2007-07

SSC, V2.1

The Receive FIFO Control Register RXFCON (only available in SSC0) contains control

bits and bit fields that determine the operating mode of the RXFIFO.

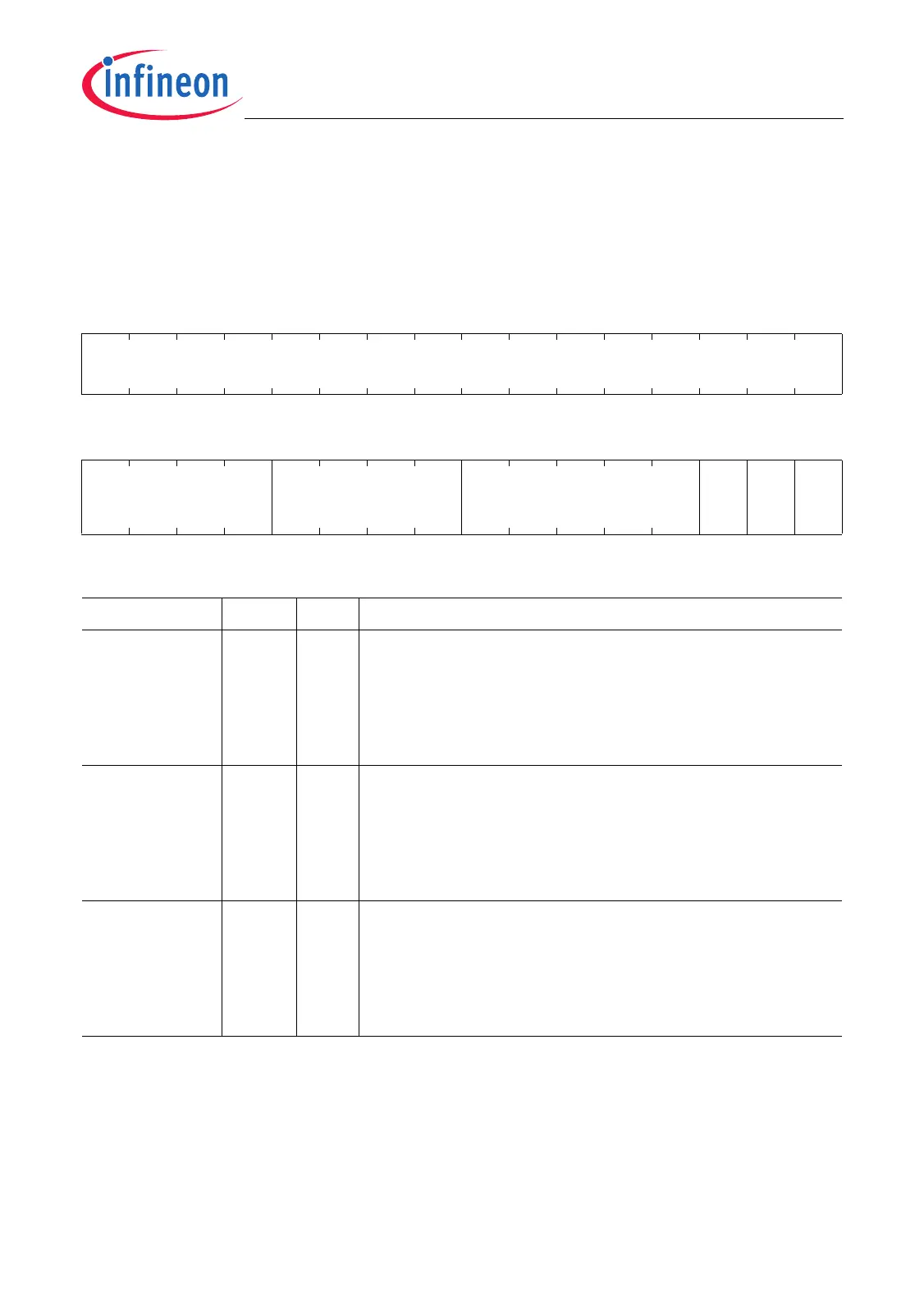

SSC0_RXFCON

SSC0 Receive FIFO Control Register (30

H

) Reset Value: 0000 0100

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0RXFITL 0

RX

TM

EN

RXF

FLU

RXF

EN

r rw r rwwrw

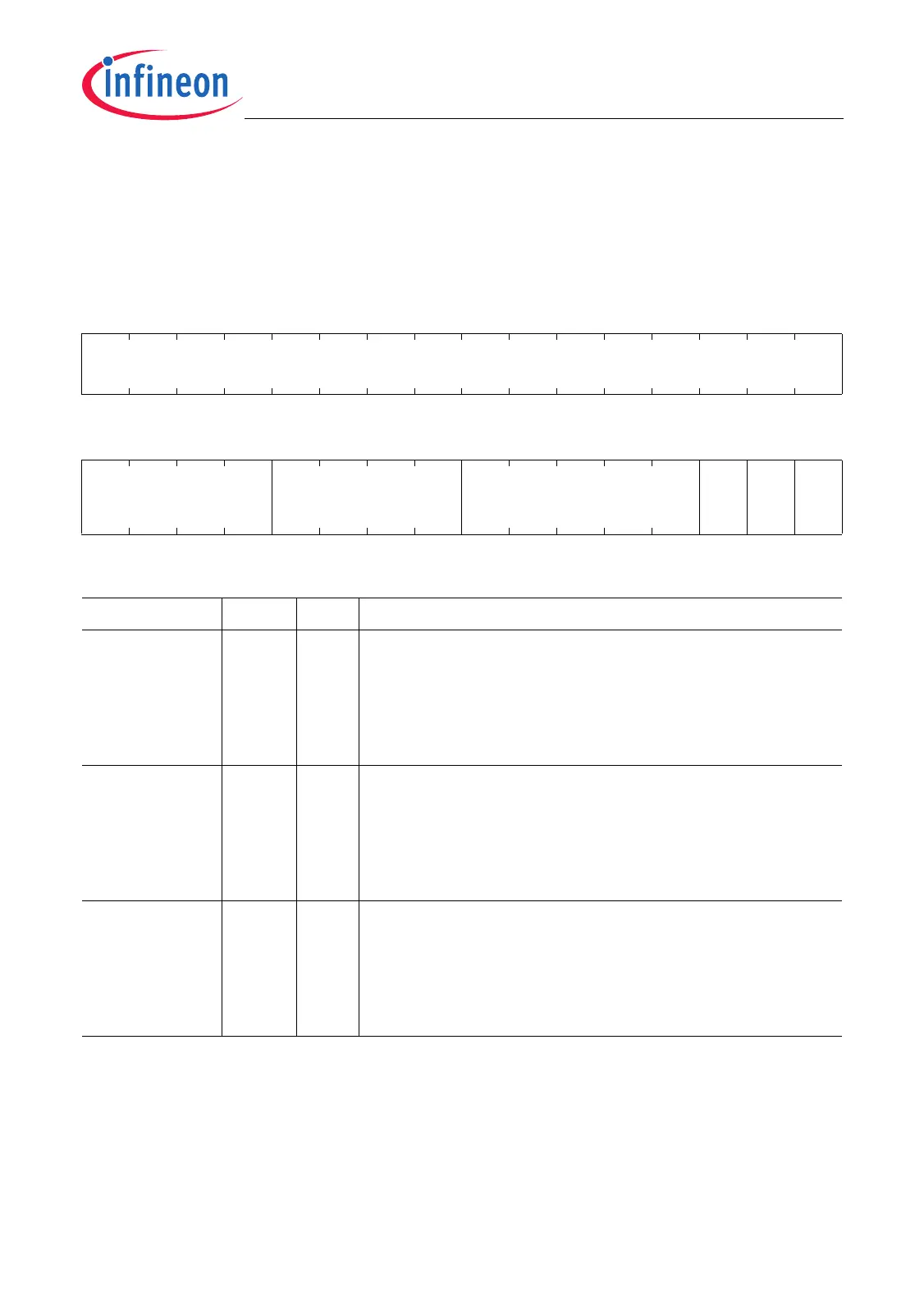

Field Bits Type Description

RXFEN 0rwRXFIFO Enable

0

B

RXFIFO is disabled

1

B

RXFIFO is enabled

Note: Resetting RXFEN automatically flushes the

RXFIFO.

RXFFLU 1wRXFIFO Flush

0

B

No operation

1

B

RXFIFO is flushed

Note: Setting RXFFLU clears bit field RXFFL in

register FSTAT. RXFFLU is always read as 0.

RXTMEN 2rwRXFIFO Transparent Mode Enable

0

B

RXFIFO Transparent Mode is disabled

1

B

RXFIFO Transparent Mode is enabled

Note: This bit is “don’t care” if the RXFIFO is disabled

(RXFEN = 0).

Loading...

Loading...